Hello,

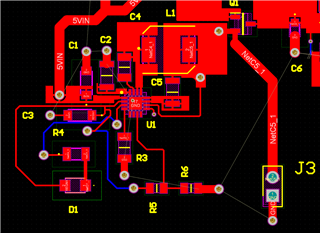

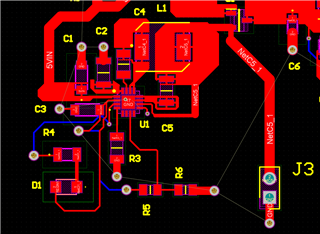

Please review my pcb layout.

I have not made a ground polygon pour yet to connect all ground connections due to difficulty seeing traces and components after pour on the bottom layer.

Thank you,

Andres Perez

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

Please review my pcb layout.

I have not made a ground polygon pour yet to connect all ground connections due to difficulty seeing traces and components after pour on the bottom layer.

Thank you,

Andres Perez

Hi Andres,

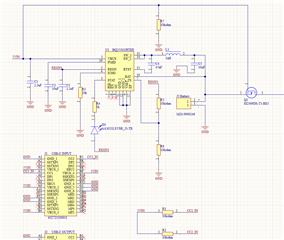

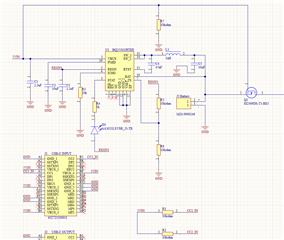

Schematic Review:

1. Confirming 4.2 charge voltage limit and 2 A charge current.

Layout Review:

1. I would try and see if you can move the PMID capacitor closer in. This could involve maybe moving the BTST capacitor a little further to the right.

2. It is important to place the REGN capacitor as close as possible to the pin. The via for the STAT pin is lower in priority than the REGN capacitor placement.

Regards,

Mike Emanuel

Hi Mike,

Yes confirming a charge voltage of 4.2 with a charge current of 2A.

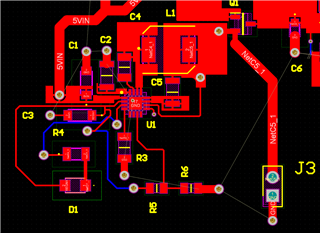

Here are the changes I have made.

Please see if this would be better or if there's still changes to be made.

Thank you,

Andy

Hi Andy,

You can also move VBUS cap closer to the IC. No need to have all that extra pour on PMID to the left of the cap.

Regards

Hi Andres,

The only room for improvement is to use smaller capacitors as you are able. Please compare with the BMS005 REV A. The size of some of the capacitors seems larger than what we use on our EVM.

Regards,

Mike Emanuel