hello.

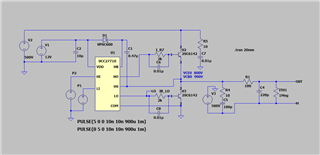

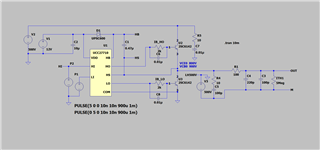

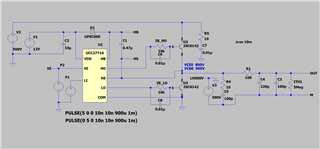

I am considering a chopper output circuit using UCC27710.

The switching element uses a bipolar transistor to reduce noise.

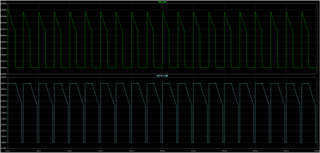

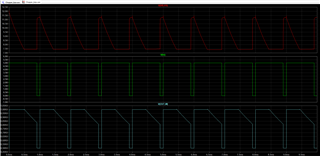

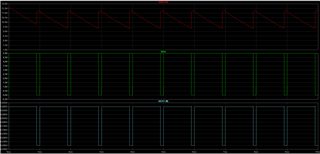

I'm using. When you operate it, the base current will drop from the middle,

The output voltage will drop.

Is there a current limiting circuit on the HO output of UCC27710? if there is

What is the upper limit current?

Thank you.