Hi,

UCC28070 is being considered as a circuit for the three-phase Full-wave rectification PFC.

I understand that UCC28070 does not support DC input because

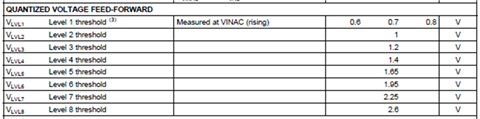

the IC needs to set the correct multiplier level using the VINAC input.

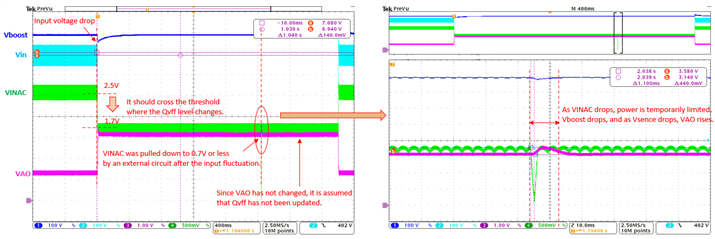

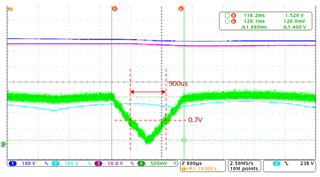

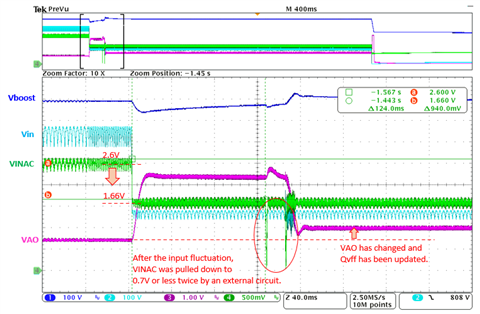

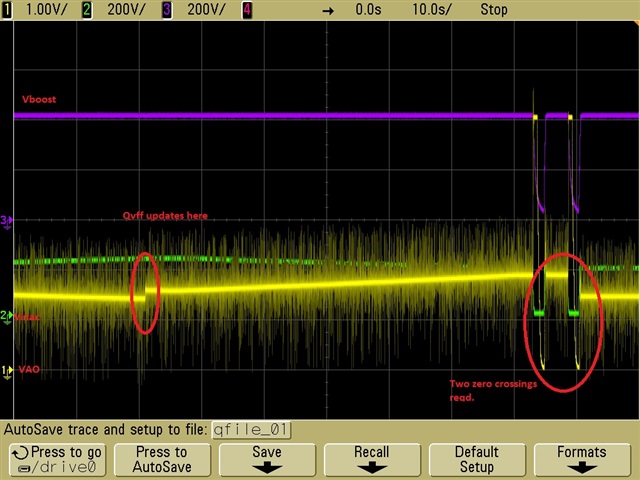

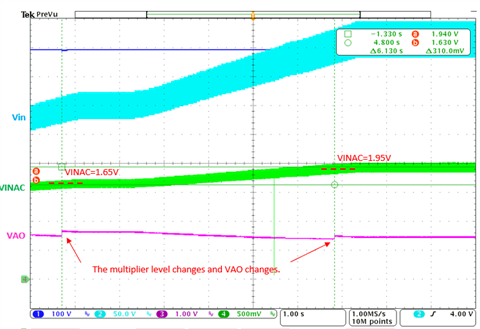

However, as shown in the waveform below, we have confirmed that the multiplier level changes when VINAC is always above 0.7V.

CH2_Vin , CH3_VINAC , CH4_VAO

Changes in VAO occur when VINAC crosses thresholds such as 1.65V and 1.95V. Only when VINAC crosses from a low value, there is no change in VAO when changing from a high value to a low value.

I have the following question.

1.Does VINAC have to drop below 0.7V to update the multiplier settings?

2.Can the multiplier settings be updated without VINAC dropping below 0.7V as in the waveform above?

If it occurs, please tell me the control sequence.

The following questions assume that the multiplier settings can be updated by dropping VINAC below 0.7V.

3.Can we set the correct multiplier level by dropping the VINAC input below 0.7V from the outside?

4.When VINAC drops below 0.7V, what timing input information is used to update the settings?

For example, information about 2 seconds before dropping below 0.7V.

Best regards.