Other Parts Discussed in Thread: TPS65987,

We have a design that can be powered from either USB-C or a barrel jack. We want to support seamless switching / failover from barrel jack to USB-C power, but don't have space on the board for an additional power ORing / or ideal diode controller. The barrel jack input protection circuitry has a power good output, which is routed to pin GPIO20 and configured as "barrel jack detect event" on the TPS65987 . The TPS65987 uses internal powerpath PP1 for the sink profile. In the configuration tool, under "port control", the "sink control bit" is set.

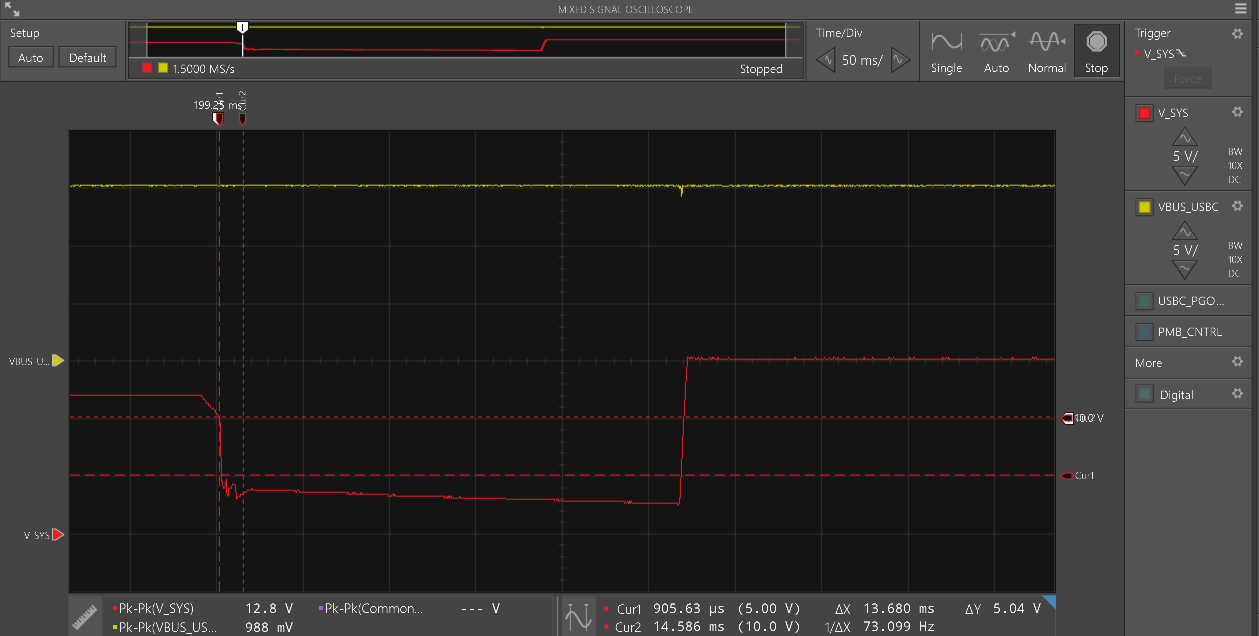

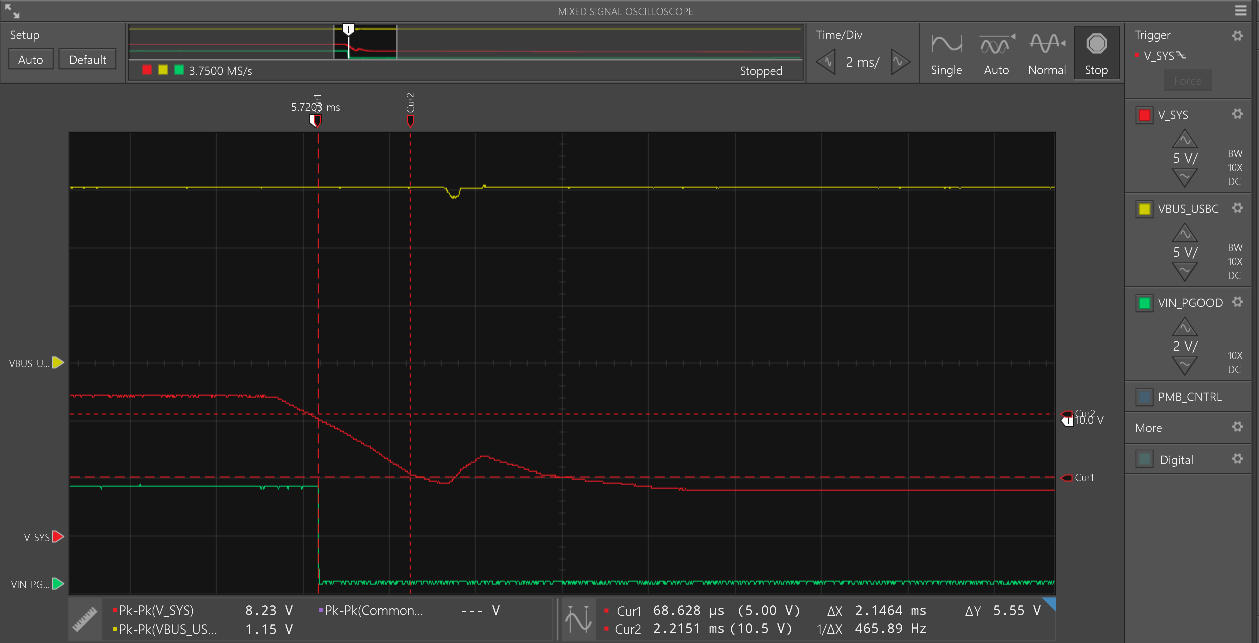

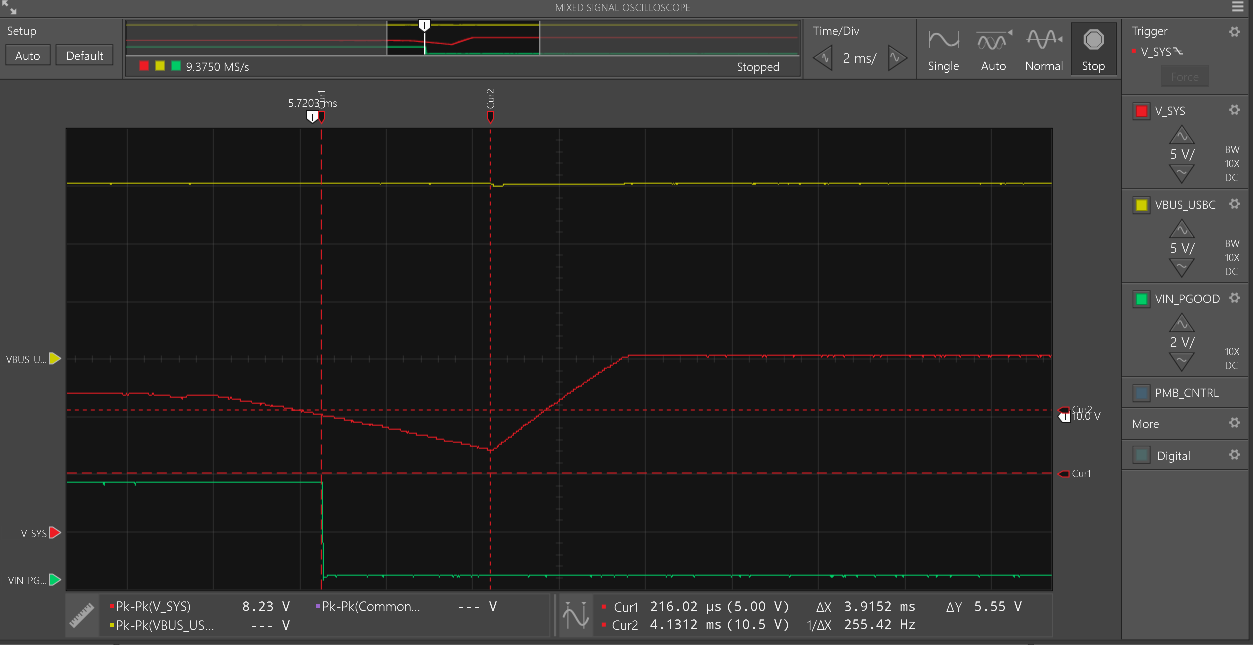

With this configuration, the board works fine with either USB-C or barrel jack power individually. When both are inserted, the TPS65987D correctly detects the barrel jack PGOOD signal and opens its internal powerpath, and the board can seamlessly switch over from USB-C to barrel jack power. However, if both power sources are present, and the barrel jack is removed, it appears that the powerpath is not closed fast enough to maintain board power.

- The barrel jack power source is nominally 12V, power failure detection threshold is around 10V, and the board can operate down to 5V. We support USB-C PD profiles between 9V-15V. Given the capacitance board, it takes around 1ms for the voltage on the input rail to fall from 10V to 5V and other regulators to start dropping out, resetting the board.

- We see that when the board is powered from a barrel jack, and then a USB-C PD source is connected, a valid profile is correctly negotiated, the source provides the expected VBUS voltage, and the TPS65987 correctly keeps its internal powerpath open. (If the "sink control bit" is not set, the powerpath is immediately closed and the USB-C source can back-feed the barrel jack supply -- this is not desirable behavior; we want to prioritize operation from the barrel jack and failover to USB-C only when barrel jack is not present, allowing for example users to use a USB-C battery bank as a backup supply)

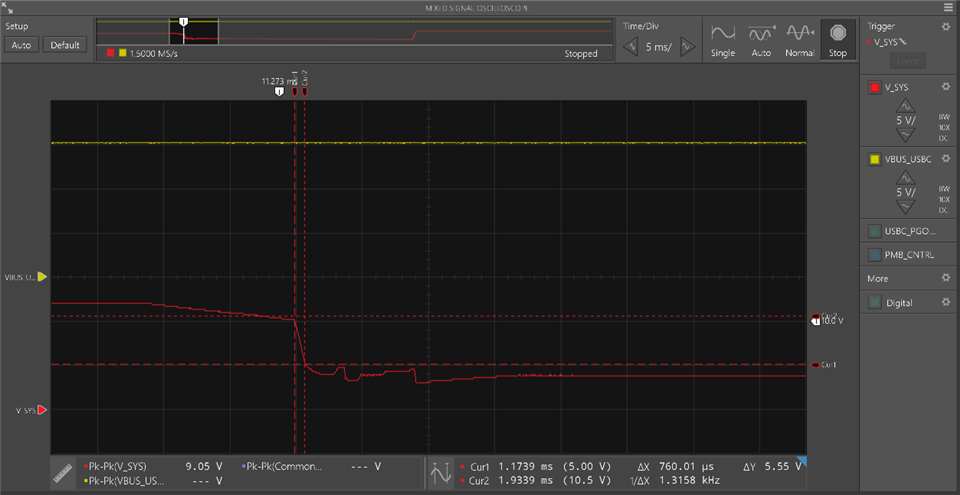

- In the above state, when the barrel jack is unplugged, the PGOOD signal is deasserted at the expected voltage level. However, the TPS65987D takes too long to respond to the event and close the powerpath. This needs to happen within the ~1ms window before the voltage decays to the point that other rails start dropping out, but it seems to take several milliseconds minimum and the board generally loses power, resets, and then reboots on USB-C power.

- We have already set the "Soft Start Slew Rate" setting under "Port Configuration" to the maximum, 3.39V/ms.

Is there anything we're missing in the configuration to either (a) disable soft-start entirely, (b) make the TPS65987D respond to the barrel jack detect even faster, or (c) otherwise increase the speed of failover to USB-C power? Our board is quite space-constrained, so it's unlikely that we'd be able to add an independent power ORing controller, or substantial additional capacitance to hold up the system rails for longer, and we were hoping to achieve this with just the functionality of the TPS65987D.