Hello TI-Team,

This is a question when the UCC28782 operates in QR mode.

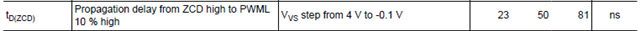

I assume that ZCD is detected at the VS pin, but how is the delay time from ZCD detection to PWML output determined?

Is it possible to change the delay time?

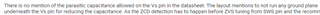

Does it mean that the delay time cannot be set because the VS pin only divides the AUX winding voltage with resistors?

Also, are you aware that the time from PWMH off to PWML on in ACF mode (that is, tz) is the tz set by the RTZ pin?

Is the delay time at QR unrelated to that?

Kind regards

TETSU