Hi,

We are using this isolated driver (UCC21225A) in shunt pwm dimming for led string. LED's are driven by constant current source Representative schematics attached

1) Here the series regulator never get reverse biased , since vdd always higher than MID point voltage (clamp by LED parallel with dimming mosfet), Series regulator always supply energy to boot cap.

- Does the general rule of thump of Cinput= 10x CBoot apply here?

- Do we even need a capacitor at the collector terminal (Cinput) of series regulator transistor?

2) In the datasheet, he output pwm drive has an absolute maximum rating of -0.3v . If it exceeds (Negative going Spike< -0.3v) what is the failure mode,

- Does the device latch to a certain state or will it get damaged?

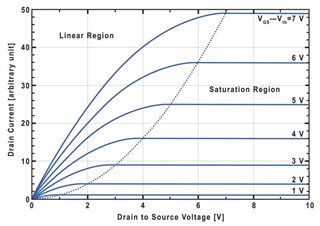

3) Can you think about a failure mechanism involving this chip , where this chip can take mosfet (high side or low side) out of saturation region to linear region and increasing its power dissipation?

Jacob