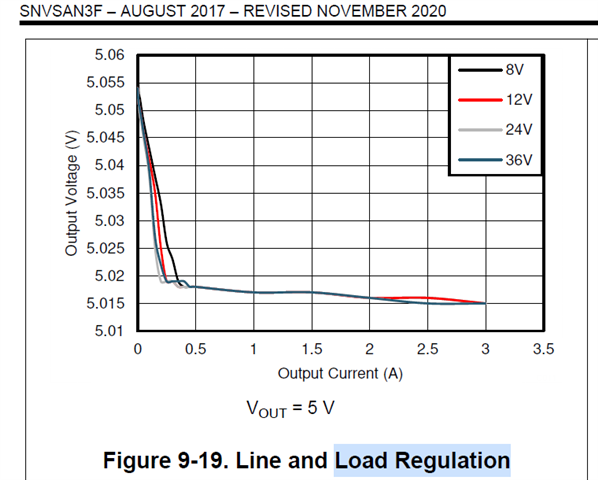

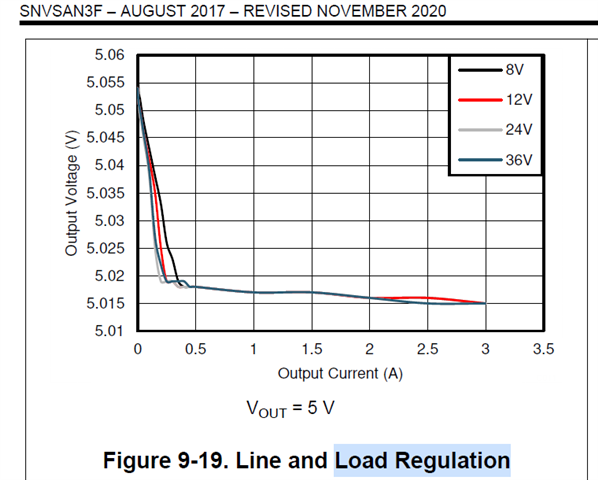

Hi team,

As shown in the figure, what is the reason for the increase in load and the decrease in output voltage? ( except line loss), Expect a detailed explanation. Thanks

BR

Sveinn

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

As shown in the figure, what is the reason for the increase in load and the decrease in output voltage? ( except line loss), Expect a detailed explanation. Thanks

BR

Sveinn

Thanks, What about fixed-frequency ICs? It seems that the larger the load, the lower the output voltage.

And your common name is Andy (Wide Vin) Chen? I would like to learn more about this issue to you.

B R

Sveinn

Hi Andy, why " The lower the Error Amp output which will drive the switching clock to more lower end " Can you explain it in conjunction with the block diagram?

B R

Sveinn

Hi Sveinn,

This is behavior of PFM version converter, The Fixed PWM version converter will regulate output more tightly.

Sorry that this control loop was not shown on block diagram because of proprietary IP, you may found some introduction on its data sheet.

B R

Andy

Hi Andy,

Thank you very much for your detail reply.

But I still have some doubts about FIX PWM version converter. In the actual product, we also see higher load, Lower Vout, Is this really just because of line loss ?

B R

Sveinn

Hi Sveinn

PFM version has same output regulation as FPWM version at non light load condition, for Peak Current Mode control, the EA output determines the inductor current peak which proportional to load current, so at heavy load condition, Vout will be slightly lower, then the EA can output higher voltage to drive inductor current higher to meet load current requirement

B R

Andy