Other Parts Discussed in Thread: TPS568215

1. Can you provide voltage regulator output waveform when marginning is enable (high or low)

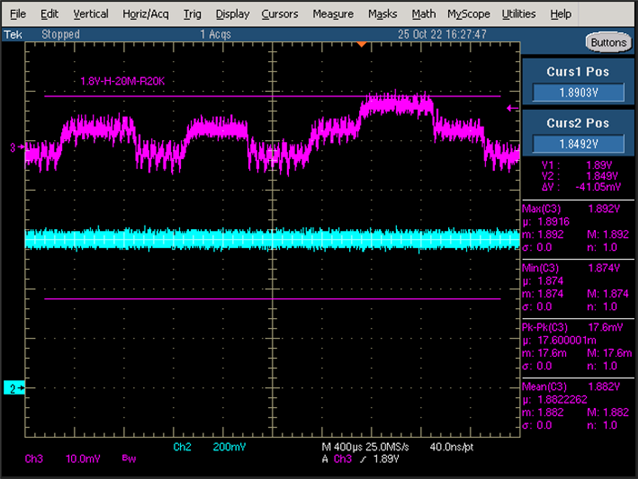

2. Following is what I captured for 1.2V output waveform with 1.2V offset when margining is enable high. Is it normal to have many spikes (overshoot and undershoot)?

3. 1.2V has also fed back to Amon pin,Is there any way to calibrate or offset for Amon pin?

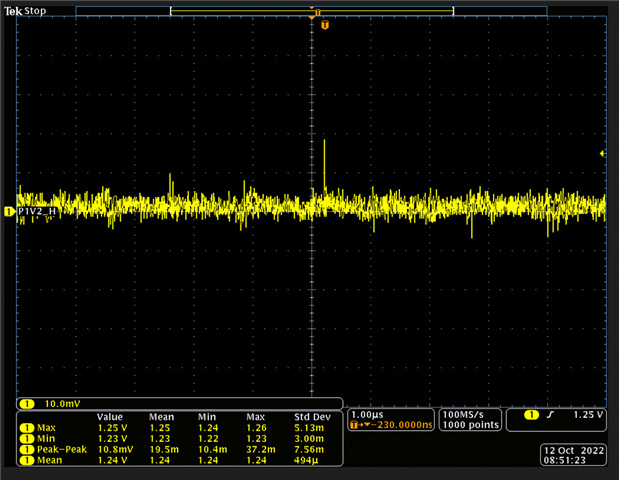

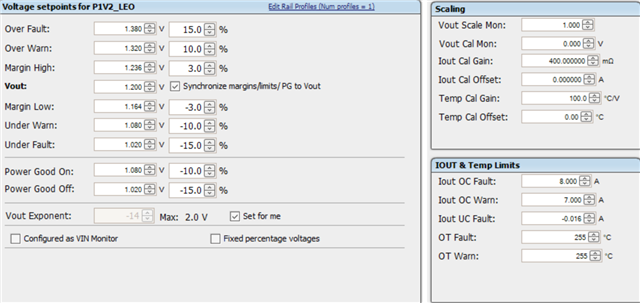

4. As shown in second photo below I have set +/- 3% margin high and low for 1.2V ( range 1.236V ~ 1.164V). However you can see actual measurement is over spec (1.25V > 1.236V).

It does not seems right, Can you explain why 1.2V margin high is over +3%?

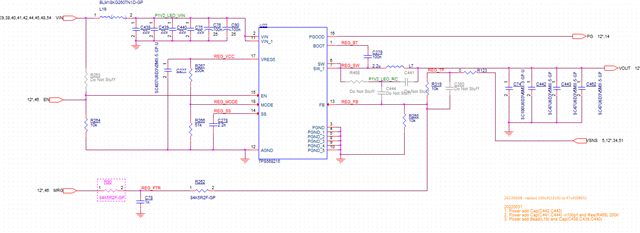

PS. Power rail 1.2V schematic is attached with margining circuit

Mike Hsu