We have a requirement of keeping WDO output logic low upon timeout. Since the output open drain and is pulled up so getting pulses with timeperiod of 1.6 sec. Please let us know if there is any way to keep the WDO output logic low upon timeout.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

We have a requirement of keeping WDO output logic low upon timeout. Since the output open drain and is pulled up so getting pulses with timeperiod of 1.6 sec. Please let us know if there is any way to keep the WDO output logic low upon timeout.

Hi Aditya,

Thank you for your question, I'll be happy to help. I just want to clarify, you want to latch output of WDO so that WDO stays low indefinitely?

Jesse

Hi Jesse

Yes exactly we want to latch WDO output upon timeout.

Thank you for your quick response.

Regards,

Aditya

Hi Aditya,

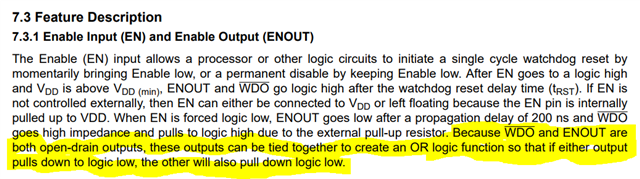

Thank you for the clarification. The TPS3431 is self does not have a Latch function, but it can be emulated by holding the EN pin low and have ENOUT connected to the WDO pin. While in this state the WDO pulse will not occur. This can be implemented in various ways. Such as using GPIO pin for a simple solution or using a full external latch circuit.

Jesse

Hi Jesse

Thank you for update.

If i keep en pin low then both ENOUT and WDO output will be in tristate which will eventually be pulled high via external pull up.

Please confirm if i make en low & tie WDO with ENOUT then after time out the WDO will stay low.

Regards,

Aditya

Hi Aditya,

Please refer to the datasheet snippet below for the confirmation.

Jesse