Hello, I am using the LM5060. I have had similar issues with the evaluation module and my own prototype.

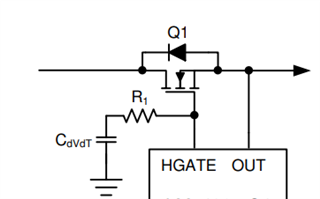

First i modified the evaluation module to resemble this:

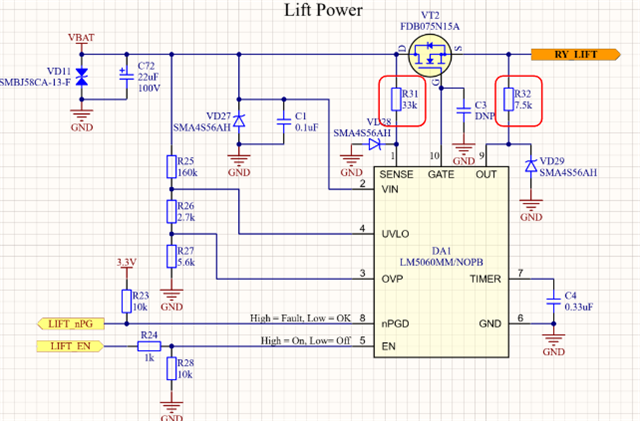

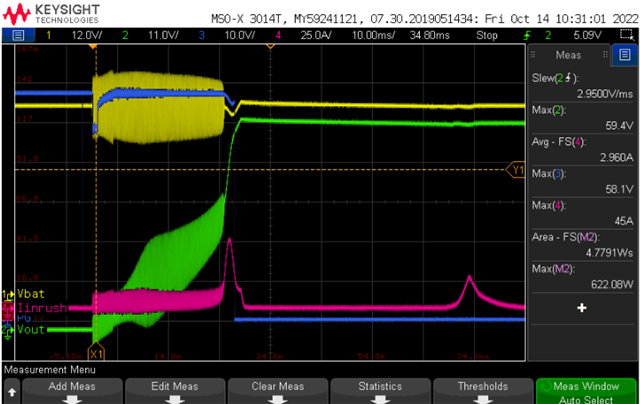

The issue i had is my load is very capacitive in nature and can generate inrush of upto 90A without including any dv/dt slow down as shown here:

Note: The yellow waveform droops in the beginning because it is powered from PSU which hits power limit at that level and reduces voltage alittle bit. For the purpose of this investigation lets ignore it for now.

As it is, the FETs are very close/slightly over it's SOA limits and so i added 4700pF capacitor for C3.

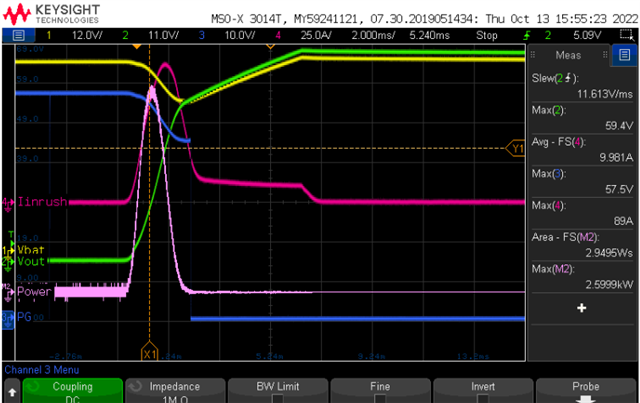

However when i did this there was a lot of ringing added into the system (although you can see inrush is reduced).

I suspected this was because of LC resonance forming on the gate line because of the added capacitance.

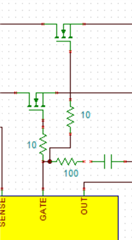

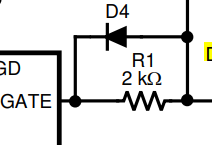

I added a 2.2k resistor on the line to damp this (without concern for slow turn on because the chip has constant current source). I also added a diode for reverse direction like this:

However this simply made my circuit fail instantly with the FET shorted from drain to source.

Could you help me debug this? Note adding a parallel mosfet which i need for continuous operation creates a similar issue for ringing.