Other Parts Discussed in Thread: TPS798-Q1

Hi Experts,

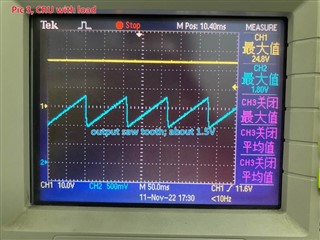

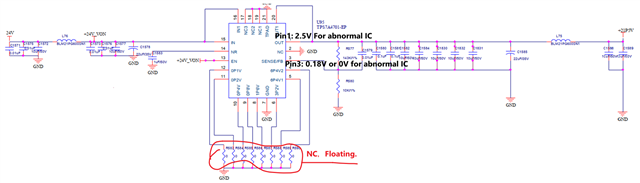

Strange phenomenon were detected by my me about the fb pin and output. Output will change to 2.5V and Vfb is 0.18V or close to 0v with the normal input voltage 24V. No abnormal heating points or burnt defect was detected on abnormal chips. Very strange, the Vfb voltage is abnormal. Once we replaced the abnormal TPS7A4701-EP with a new one, it works normally.

The input output specifications and the SCH are attached. Please kindly give me some insights about this?

|

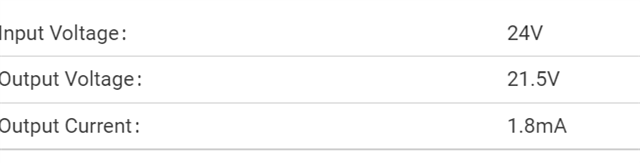

Input Voltage: |

24V |

|

Output Voltage: |

21.5V |

|

Output Current: |

1.8mA |

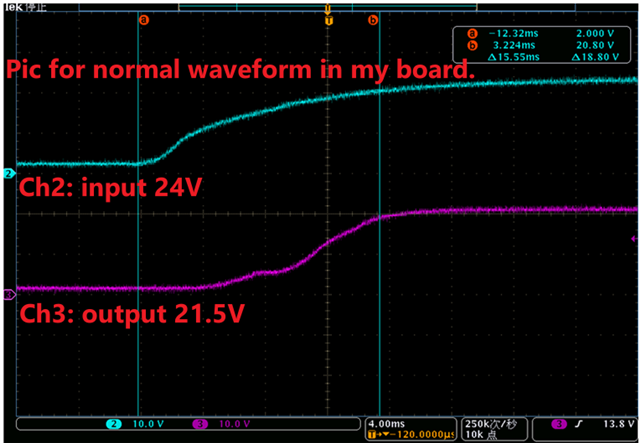

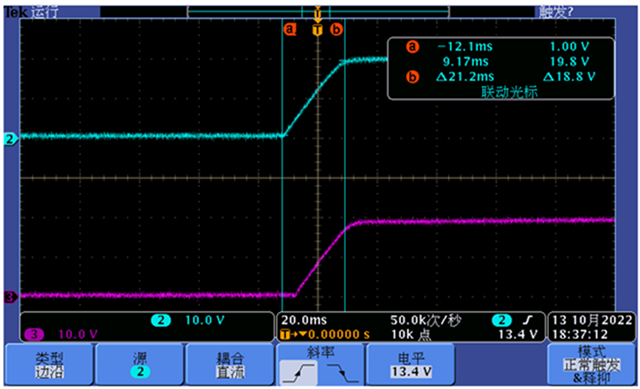

The vout voltage setup diagram for normal ICs (ch2).

Thanks ,

Marsh