Hello team,

My customer occurred the DSP reset issue while using TPS65313.

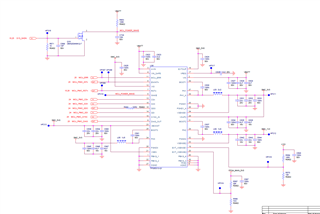

They use one simplified board (Only DSP+TPS65313 and motor driver), the SCH is as below:

Add some notes,

The connection between pin7 and DSP is cut off.

Pin 8 connect to DSP, but DSP doesn't use this function.

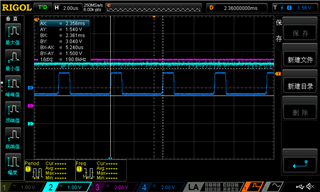

Has already masked the SCK/SDO/SDI output, only use NCS. Operate the SPI with a cycle of about 7us, that is, only the NCS signal of the SPI is switching, and the power restart will occur.

Now they don't configure PMIC, just use the default configuration. And DSP only send one SPI command 0x07 to the PMIC, and read the data from PMIC.

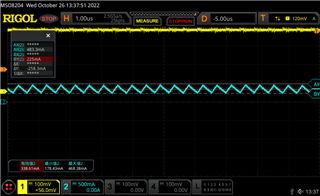

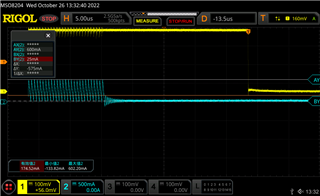

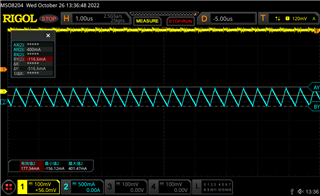

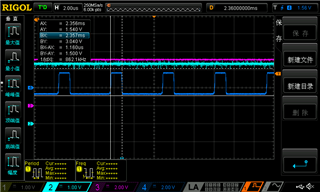

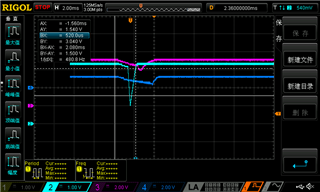

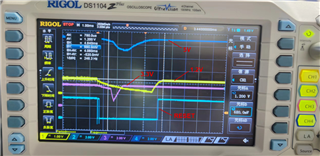

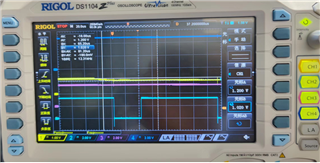

This is the waveform while resetting. Picture 1 is showed the whole, picture 2 is the zoom-in waveform. 1.2V drops a lot which may cause the reset.

SYSCLK_ERR is the only fault they have found, some register cannot show the fault status due to the reset.

These are the questions:

1. Is there any risk about the SCH that will lead to the power increase while SPI working? This may lead to the PMIC overload and reset.

2. Is there any mechanism that if the SPI is too frequent to reset the PMIC?

3. Any possible reason and suggestions need to do for them?

Thank you so much.

Best regards,

Lanxi Li