Hi Team

There is a good news that we DIN LP8866!

Could you please help confirm the design and Schematic is ok? THX

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team

There is a good news that we DIN LP8866!

Could you please help confirm the design and Schematic is ok? THX

Hi, Kygo

I will give you a feedback by email for this case.

Hi Zhiqian

I have updated the design tool ,THX

LP8866-Q1_Design Tool_for Publish_Final_Protected(xg) Ver.01_TI_1027.xlsx

Hi Zhiqian

Thank you for checking the SCH!

For the Gain Margin result is OK? THX

Hi, Kygo

This is the Gain Margin gap, not the gain margin.

This value is fine for the calculation tool.

Hi Zhiqian

For LP8866 issue

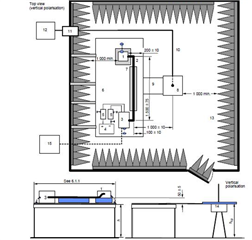

FSW = 400KHz; the frequency multiplication after spreading is affected at 800KHz, 1200KHz, 1600KHz!

At present, it is confirmed that it is affected by LP8866. Customers have tried FSW = 200KHz, 303KHz, and 500KHz frequency multiplication, all of which affect this frequency band.

Test method CISPR 25 / Radiated emissions from components/modules - ALSE method

In addition, I would like to ask what is the upper limit of RG in Datasheet Table 8-3?

Hi, Kygo

I cannot understand your request clearly.

RG limit is related with FET, at least FET can work normally.

Hi Zhiqian

Thank you!

Currently I have the following approach:

HI, Kygo

RG will influence the rising time and falling time of GD.

You can check if the lower rising time can be accepted by FET and estimate the ripple influence of boost.