Other Parts Discussed in Thread: TPS785-Q1

Hi,

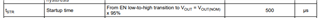

A issue about the startup time of TPS746EVM-009 that we need your comments:

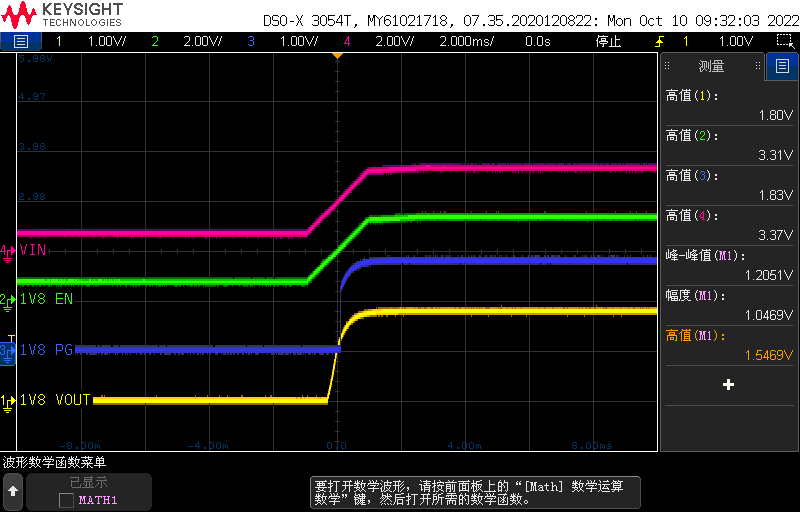

1. Without any load, the startup time of the EVM is quite small;

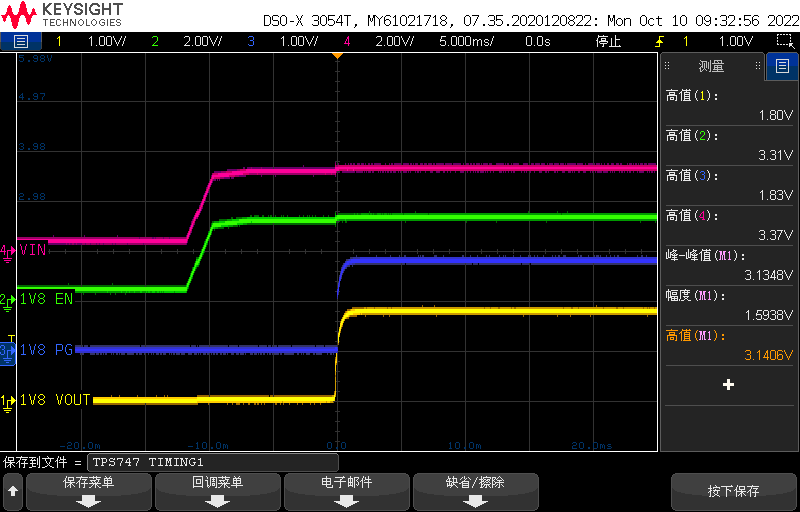

2. With 10mA load, the startup time is about 10ms;

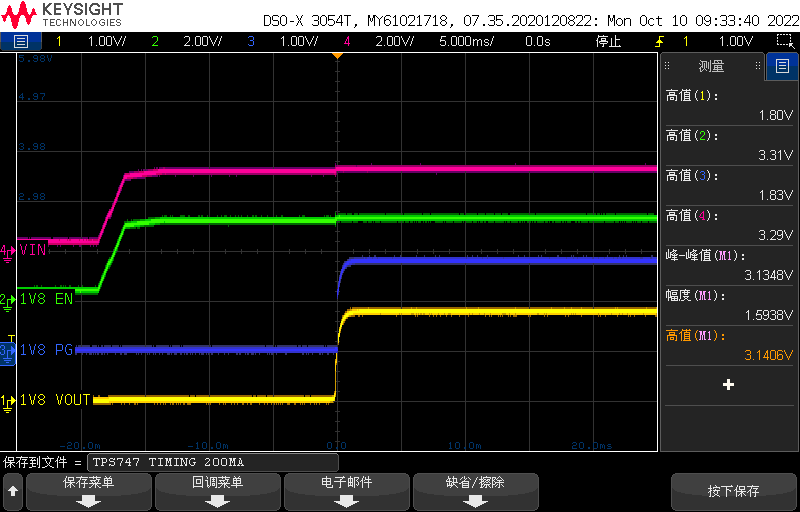

3. When the load is 200mA, the startup time increased to 17ms;

It seems that the startup time of the chip will be infulenced by its load, this is inconsistent with its specification(500us).

We need your help to analyse the test data and want to know whether there is a way to reduce the startup time.

Test condition: VIN = 3.3V; VOUT = 1.8V.