Hi team,

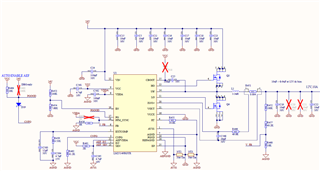

we recently got issues with LM25149 behavior during startup.

Vin:24V

Vout 12V

Fsw 600kHz

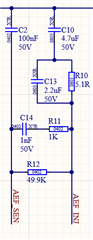

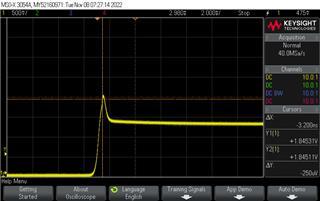

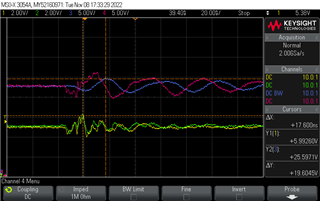

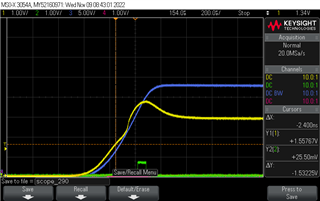

Symptom is that board fails to power-up. Power consumtion is either 22mA or 160mA (rest of the board is pretty much powered down). Trying to isolate problem we found that issue is caused by AEF probably overloading the Vcc.If R461 is desoldered, board starts normally. The pin does not seem to have a short to GND pad when measured with ohm meter.

The C565 was verified on the first failing board and nothing suspicious was found. Seem to be really in the IC itself. Today, a second board developed same issue. In both cases, this happened when board was powered on after being powered off for some time, not when runnning. Before failing, nothing was done around this part of circuit, so unlikely a scope probe slip.

Any idea what could cause this behaviour? Would it be possible to send the failing chips for analysis?

We currently run two batches of boards up to now. It was not observed int he first batch that was deeply verified, but there was a limited number of samples (less than 5).

In this second run, two boards developed this issue. This was likely assembled from a different reel. Both batches of chips were obtained from TI. Difference between two batches that come to mind are COMP loop componnet values and aef values, otherwise not much was changed.

I will tomorrow investigate heatthy board for any clues, but in the meantime any advice is appreciated.

Thank you