Hello,

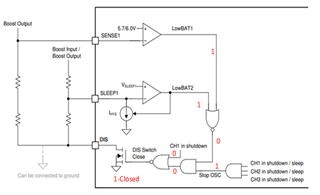

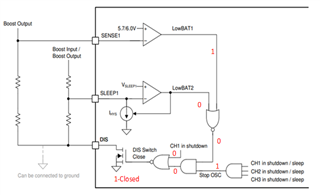

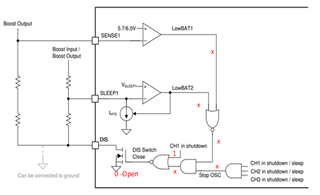

There is Sleep Mode for VOUT1 when it is configured as boost. This is explained in the pin description in p.5 of the datasheet as "When CH1 is configured as a boost, it is allowed to enter sleep mode when SLEEP1 is greater than 1.0 V". What senario is expected here? In what situation SLEEP is greater than 1.0V and less than 1.0V?

Thank you.

Regrads,

Oguri (TIJ automotive FAE)