Hi team,

My customer met a question in using TPS7B4253QDDARQ1. They want us to give explain about a non-monotonic startup and get rid of non-monotonic startup.

The circuit schematic is as follows

1.Design parameters. Vin=6V, Vout=5V.

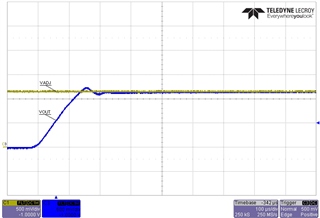

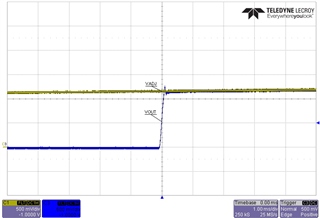

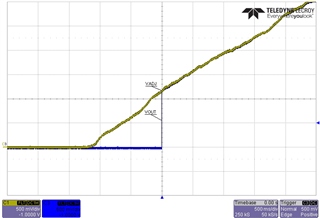

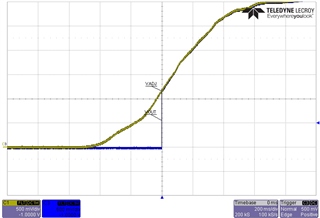

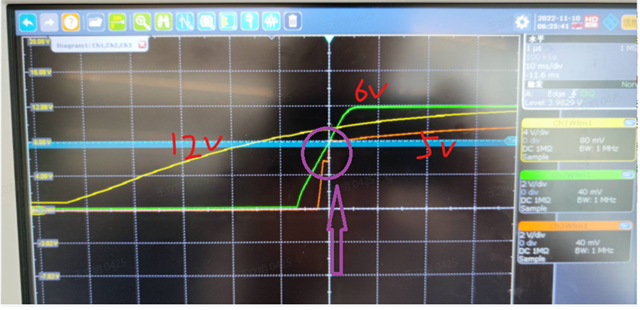

2.In the case of 5V OUT without load, there is a step to measure the instantaneous waveform of power-on. (Vin=6V The 12V is referenced to the ADJ through a voltage divider)

3.Remove Z110, Z41, disconnect F2, short FB and OUT pins in turn and there is no improvement, please help confirm the cause and improvement measures.

B R

Sveinn