Hi Team,

Good day!

What is the min voltage ramp rate (i.e. fastest rise time) on the VDD or Sense inputs?

Best regards,

Jonathan

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

Good day!

What is the min voltage ramp rate (i.e. fastest rise time) on the VDD or Sense inputs?

Best regards,

Jonathan

Hi Jonathan,

Thank you for your question. The maximum slew rate would be 1V/us for both VDD and SENSE pins.

Jesse

Hi Jesse,

So that translates to a 5V VDD can have a rise time (ramp) of 5us without any issue. Is that right?

Best regards,

Jonathan

Hi Jesse ,

Good day!

Here is a couple follow-on questions.

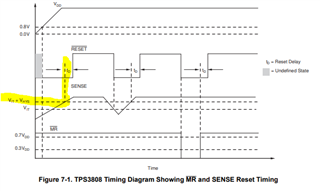

1) Datasheet table 7.6 (Switching characteristics) for reset delay listing min/typ/max mS values. If Ct is 820pF, I believe the typical reset delay time would be approximately 5.2ms. What would the minimum and maximum reset delay time be according to table 7.6? (see attached sketch)

2) Repeatability or variability question. For the same part installed, how repeatable is the reset delay from power-on to next power-on and does temperature impact the repeatability of the reset delay time? Within a particular lot purchase of TPS3808G01, are the components within the same lot relatively close in reset delay or can they vary from min to max delay?

3) From power application of VDD (5V with 1mS monotonic rise) and Sense monitoring 3.3V (10K PU and 1.5K PD), with VDD rising slightly prior to the sense voltage, does the td start when sense crosses the threshold of 0.405V (for the TPS3808G01 part)? (see attached sketch)

Best regards,

Jonathan

Hi Jonathan,

1) From table 7.6, it is ±40% from your theoretical. So with your value, you are looking at 3.12ms to 7.28ms for your min and max. This timing range accounts for temperature and other environmental factors.

2) If your are testing in a consistent environment, the time delays are repeatable. Yes, the ambient temperature does play a factor on the timing delay of the device.

3) Td starts when Vsense crosses Vit*(Vit accuracy) + Vhys. For this case, the worst will be .42525V.

Jesse