Other Parts Discussed in Thread: LM5113

Dear,

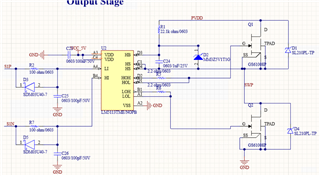

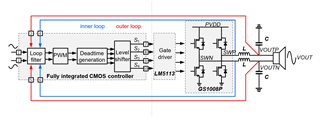

We chose LM5113 as the gate driver for GS1008P in our class-d audio amplifier (CDA), and there's a phenomenon we can't explain. We think the gate driver may cause it. Our CDA is an H-bridge structure, and the switching frequency is 1.8MHz.

The supply voltage is 50V, and the load resistance is 4Ω. A system-level circuit is attached.

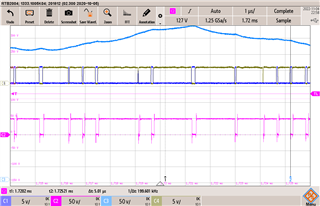

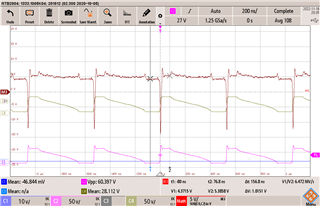

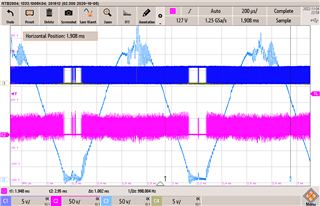

(For the attached waveforms, C1 is SL, C2 is SWP, C3 is VOUTP, C4 is SH.)

When the input of the CDA exceeds the limit (Pout=200W), the output will be clipped, that is, the top and bottom of the output waveform will be flattened symmetrically.

However, our test results (VOUTP) show asymmetry. More specifically, the lower switch of a half-bridge can be normally open for a long time when clipping, but the upper switch cannot.

We want to know whether the upper and lower paths of the LM5113 are asymmetric, or what other reasons are.

Best regards

Minggang