- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello team e2e,

I have a question regarding the "Output reset latching feature”, but it is not clear to me how to use it. Is it possible to latch the RESET output once an undervoltage is triggered. I mean keep the output “active” even if the sensed voltage goes back to nominal; and de-latch it only when commanded with a digital signal from MCU?

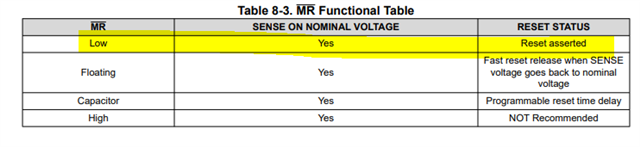

Is it via the Manual reset (MR) pin that this trigger can be sent via MCU ? My understanding is that if we connect a 10uF cap at MR pin, the programmable delay time can be set to max i.e. 1.28s, hence the RESET signal would be sent by MCU after 1.28s, is that correct ?

Also, acc to this MR functional table :

What happens if you keep the MR pin low ? What is "reset asserted"

Thank you,

Anubha

Hi Anubha,

The latching feature works such that when the RESET pin is low (asserted), it will not go high (deassert) until a predetermined voltage (please see electrical characteristics on page 8 of data sheet) is reached. This means that the RESET pin can be kept low (Reset asserted) by holding the MR/CTR pin low.

Thanks,

Patrick