Other Parts Discussed in Thread: TDA4VM

Hi BU team

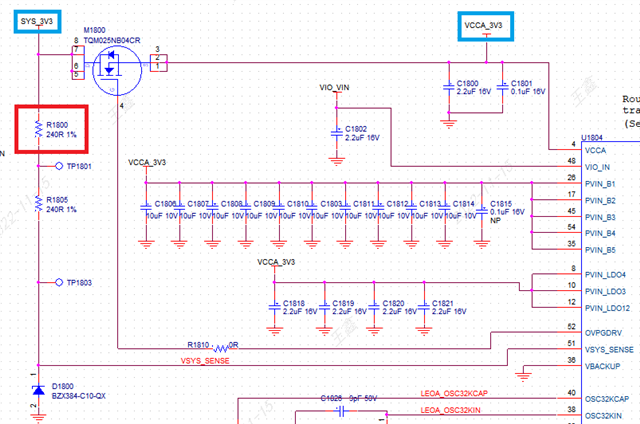

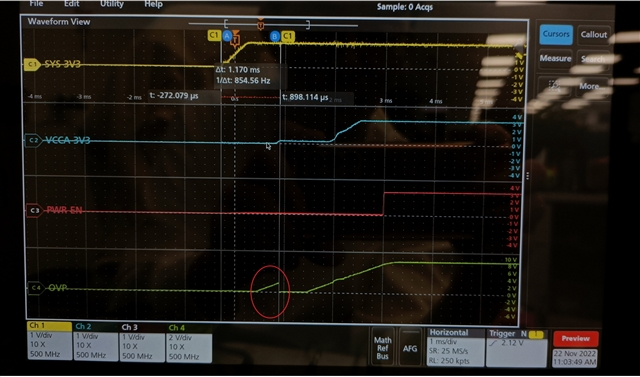

Would you help share your comments on OVPGDRV (tps65941212) behaviors when the Vsys_sense and VCCA reach 3.3V but Enable pin keep low during power up ?

Are the vsys monitor and OVPGDRV output controlled by Enable pin?

Thanks