Hi Team,

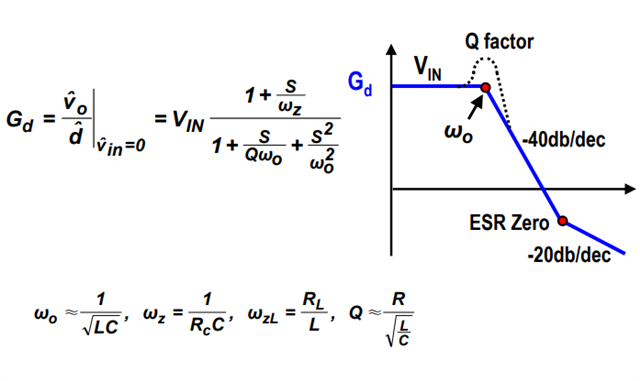

In voltage mode Buck converter control to output transfer function , here is a Q factor. I 'm not able to find the related documents clarifying Q. What does Q mean physically in Buck converter and what influence it could make to system?

Best regards,

Victoria