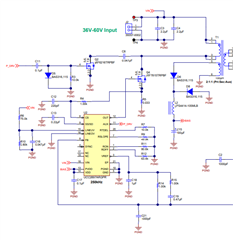

Other Parts Discussed in Thread: PMP20742

Hello,

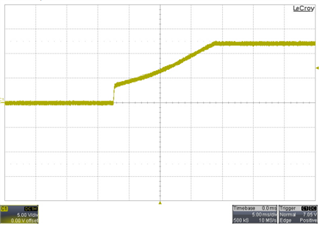

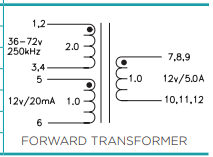

we have a design based on PMP20742 which shows a problem with the output voltage. The voltage drops, it looks like the UCC2897A goes into standby/disabled mode when this happens. The reference voltage Vref drops to zero in this case (this is seen approx. once in a second), but sometimes it also stays high.

I attached a photo from the scope, yellow is Vout, blue is Vfb, purple is Vbias

As Vbias drops belov 8V I assume, that this could be the reason for the controller to go in a disabled mode or restart. I already tried to increase the bias capacitor without success.