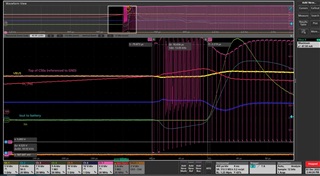

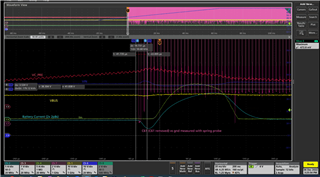

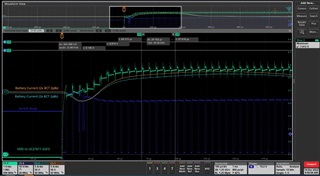

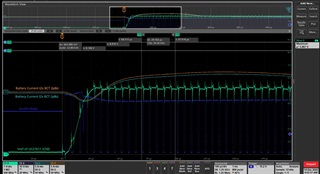

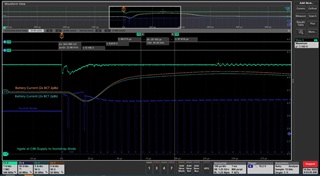

I currently have 0.1uf and 1uF capacitors on the VREF pin. The issue is that during startup in can take 76usec for the VREF to come up to 5V. This results in unpredictable switching and no switching during this time. I would like to know how small a capacitor I can use and still have that LDO remain stable.

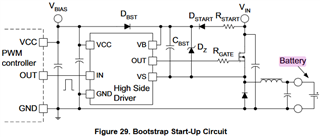

I will say the application is slightly unusual since I am using the UCC27611 as a hi side driver floating on the switch node of a buck converter. Since is a battery charger so switchnode starts above the input voltage to the UCC27611 so Cref is not charged immediately at startup until the switcher starts switching.