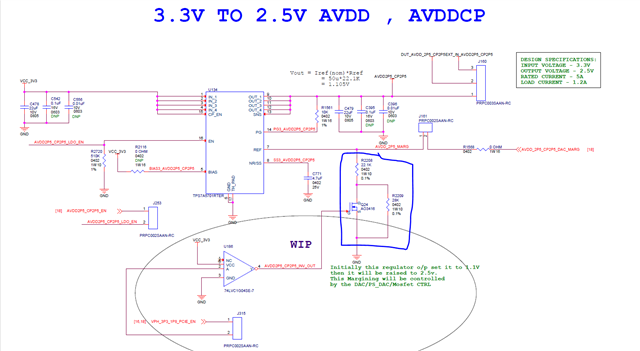

We have used this LDO in our design and below is sch for for circuit implementation.

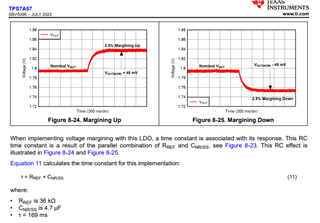

Initially this regulator o/p should be set it to 1.1V and then after 20mS it should set it to 2.5V.

To implement this, we have used the MOSFET circuit as per the below image.

Please check and provide the feedback. Also please provide us the suggestion.