Hi,

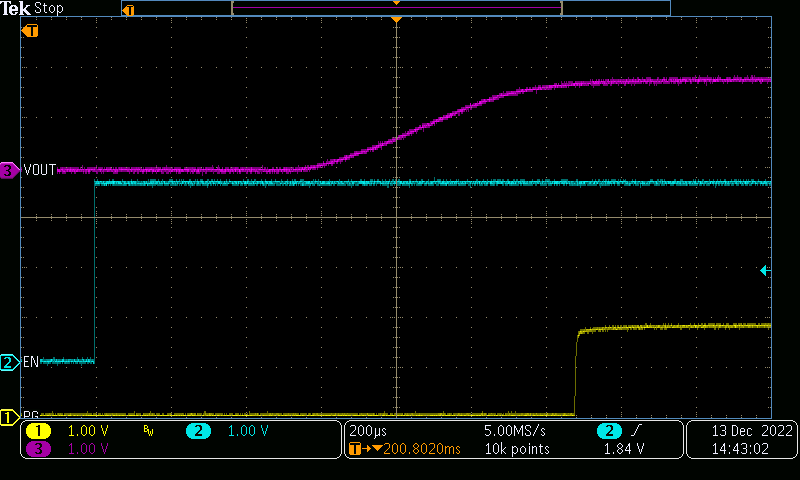

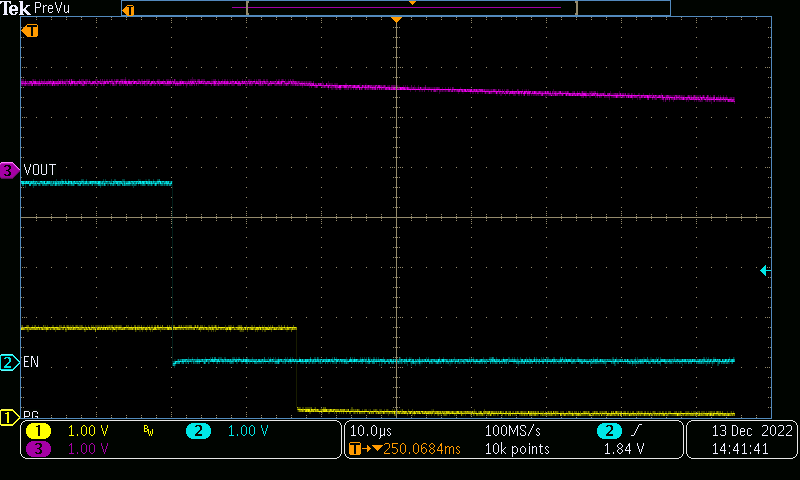

I was wondering if you knew the time it will take the PGOOD signal to go low once the EN is low.

I need this PGOOD signal low before other enable in my sequencing of converters in the power off stage and wanted to ensure PGOOD was low before other devices get turned off.

Thanks!