Other Parts Discussed in Thread: TPS62826

Hello,

Due to component shortages we redesigned the power supply in a product of ours. We are now doing automated restart tests where the product is powered down and restarted every 2 minutes as a validation.

What we are noticing is about 20 % of the DUTS fail on a TPS5432 (testbatch 30 units)

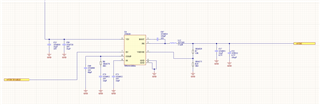

In the product we use 3 pieces of TPS5432. 2 of them make 3.3V and one makes 4V all from the same 5V. It is always the 4V converter that fails.

After desoldering the failes TPS5432 all show a short circuit between the PH pin and the GND pin measuring between 0.4 and 3.5 Ohm.

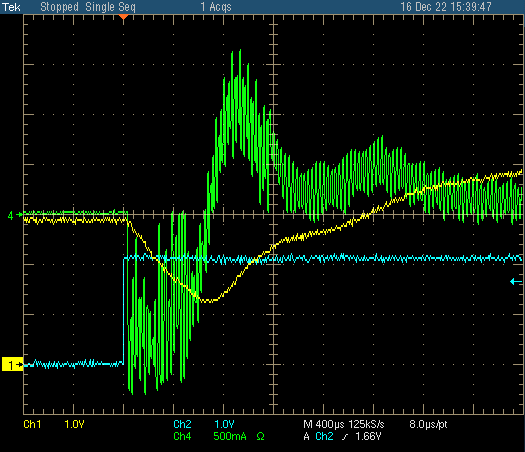

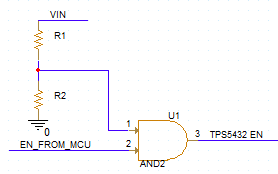

A first estimation was that maybe there could appear a to high voltage on the PH pin (allthough we could not measure this using active scope probes). As a test we added a diode on a test batch from the PH pin to the +5v input. This did not solve our problem, the issue remains.

The left converter is the 4V converter, the one on the right is a 3.3V converter

To be clear, there are no temperature issues or heavy loads that the converter needs to service.

Any thoughts on what could be causing the device failure ?

Thanks!