Hi Team,

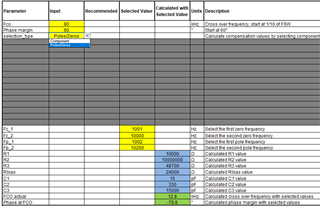

I am not sure how to select the FCO value for compensation circuit used for TPS544B25.I have read online that it should be FSW/10 or FSW/5.Can you please tell what is the thumb rule to select the FCO and pahse margin for stable loop compensation circuit.

I have attached the image of Trasient simulation.

I have attached the image of Trasient simulation.