Dear Sir

Power output: 5KW

Input voltage range: 165-270 VAC

PFC voltage: 410Vdc

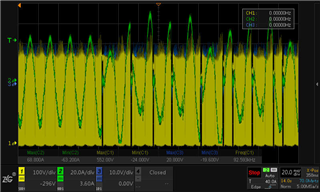

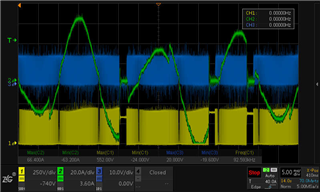

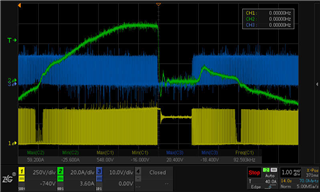

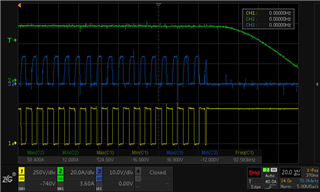

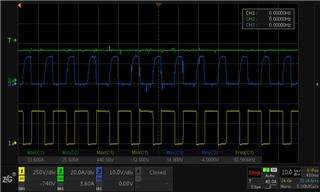

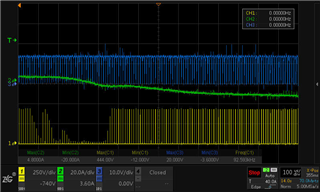

Abnormal recurrence: with full load, voltage from high voltage to low voltage test input undervoltage protection,

When the voltage is about 180Vac, the power factor drops to about 0.86 and the input current distorts.

As shown below: (1# waveform is DS waveform, 2# is input current waveform, and 3# is GS drive waveform)