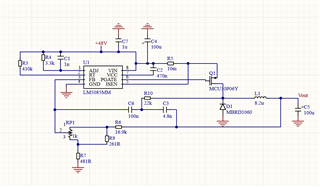

Other Parts Discussed in Thread: LM5145

Hi All,

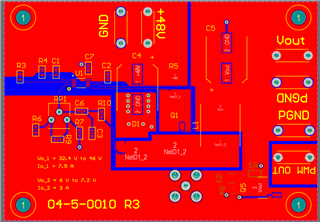

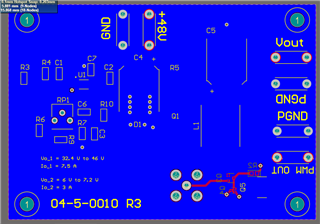

I've been working on a SMPS design using the LM5085. We have a potentiometer in the feeback loop, so Vout is variable between 32.4 and 46 V, and Iout is supposed to be up to 7.5 A.

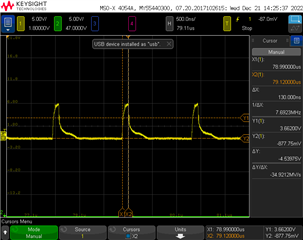

1) The load regulation isn't great. It's better at the low Vout, but it's really poor at high Vout. Vout is down to 42 V (it's supposed to be 46 V) by the time the load is 3.2 A, and it falls fast from there. This will be driving an enormous LED array, which is pretty much a fixed load, so we don't need fantastic load regulation, but at higher voltages, it will be driving a higher current.

2) The bigger problem is that at about 4 A, Vout drops significantly, and by 4.2 A it drops to 0 V. This is obviously a big problem. We probably won't need to drive to 7.5 A, but I've designed it as such for a little wiggle room, so I'd like it to operate as such. Can anyone assist me with this?