- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dears,

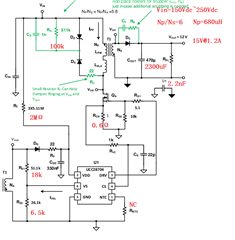

Customer feedback that when they use UCC28704 flyback power supply,Output Volatge is 15V/1.2A,when the load is light,the output is normal and when the load is heavy,the output is unstable.

Pls kindly help to check the schematic is correct or not.

Thanks

Hi Ning,

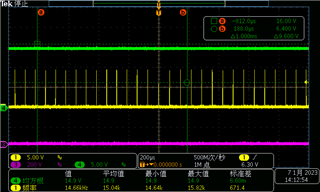

Thanks for reaching out. Can you provide a waveform of Vout, VDD, Gate(DRV) in one picture?

From the waveform you provided, it seems like FET temporarily stopped switching and therefore output drops. This happens when VDD drops below UVLO threshold (7.7V typical). If VDD is repeatedly dropping and triggering UVLO, increase CDD. (Calculations can be based on UCC28704 excel design calculator)

Can you also provide Naux winding? (Np:Ns:Na)

Thanks in advance.

Hi Ning,

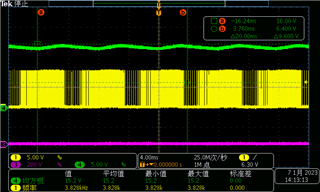

I discussed with my team and noticed that the series gate resistor is too big (Rg1=5.1ohm).

In the datasheet, it is recommended to have Rg1<1ohm.

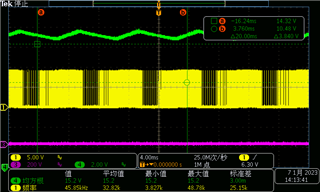

Can you also provide a waveform that includes Vout, CS, Gate(DRV) at light load and full load?

When the FET turns off, the higher series gate resistance makes it more likely that the rise in VDS will cause the FET To turn on again. This kills efficiency and may make the controller believe it is seeing an OC fault.

Dear Claire,

I will send your suggestion to customer.BTW,now we need customer change the Rg1 and provie the waveform that includes Vout, CS, Gate(DRV) at light load and full load.

I want to know if we need customer provide a waveform of Vout, VDD, Gate(DRV) in one picture and the Naux winding? (Np:Ns:Na)?

Thanks

Dear Claire,

Customer feedback that they have resolve the problem,the reason is output Cap is too big.BTW,Rg1 they will take your suggestion.

Thanks

Hi Ning,

Glad to hear that the customer solved the output ripple issue, Other than changing the output cap, did they make any other changes?

We recommend debugging by looking at the Aux, CS, VDD, Vout together. It is suggested to look at these 4 waveforms and make sure they are in line with the datasheet. If there are further questions, feel free to create E2e thread for support.

Thanks.