Hi team,

Good day.

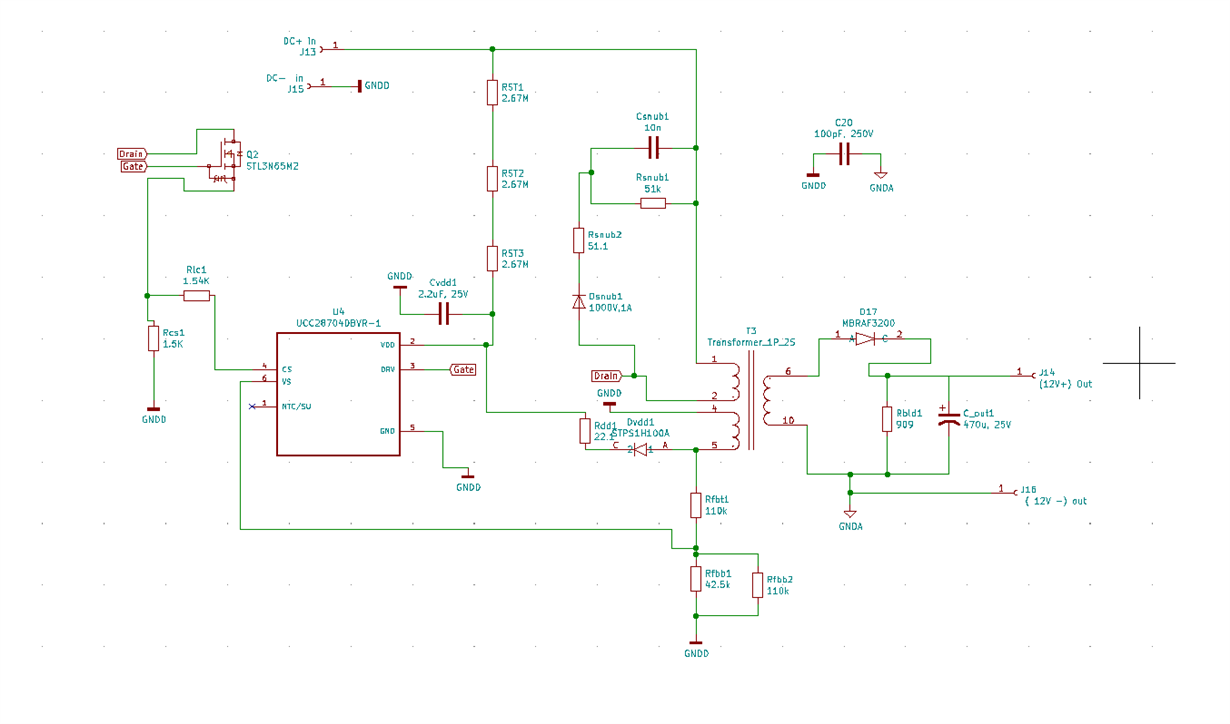

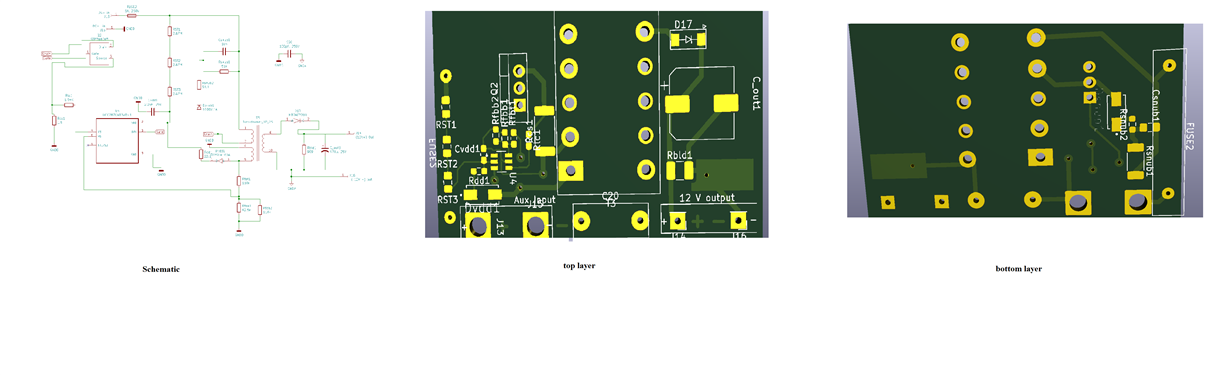

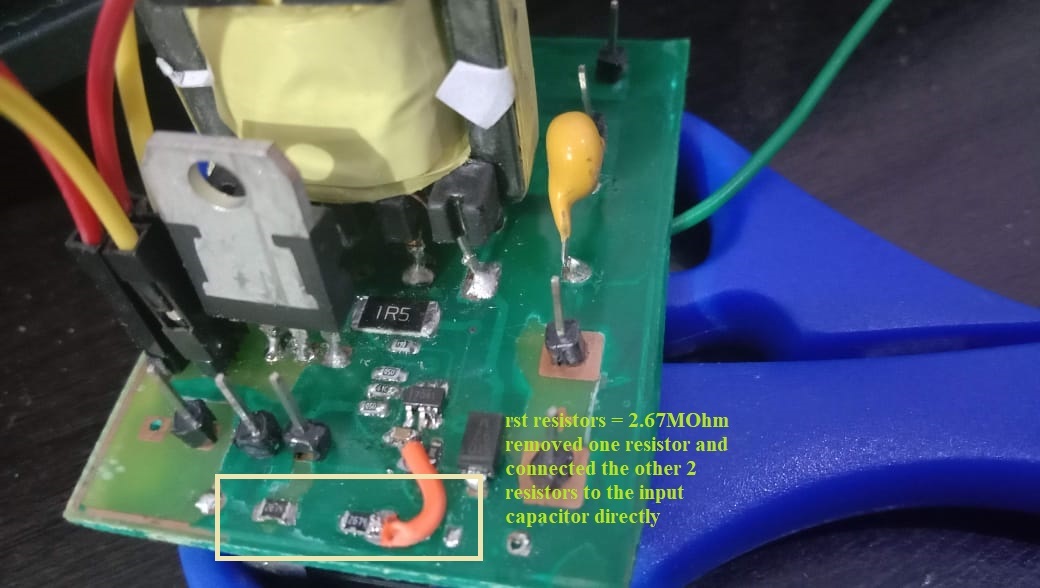

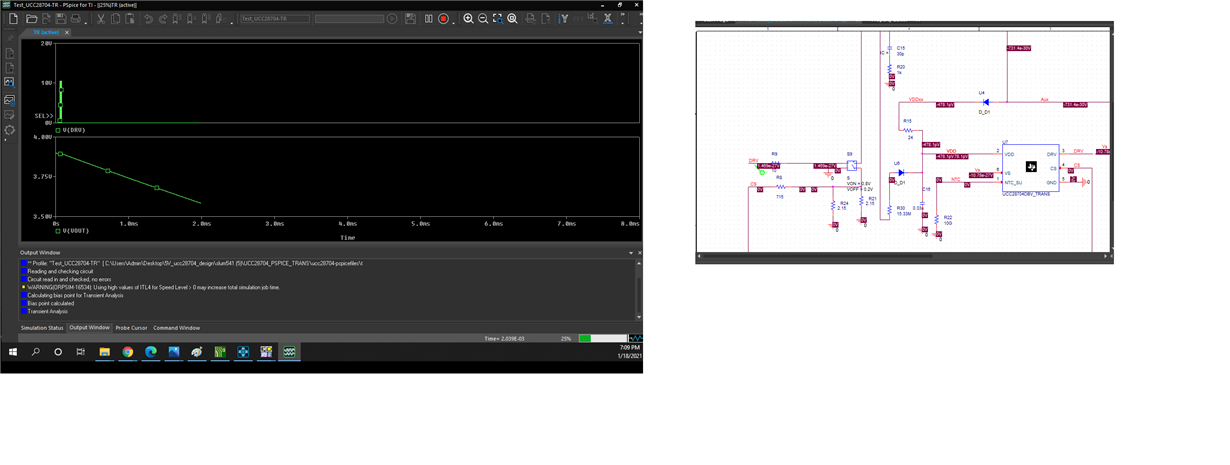

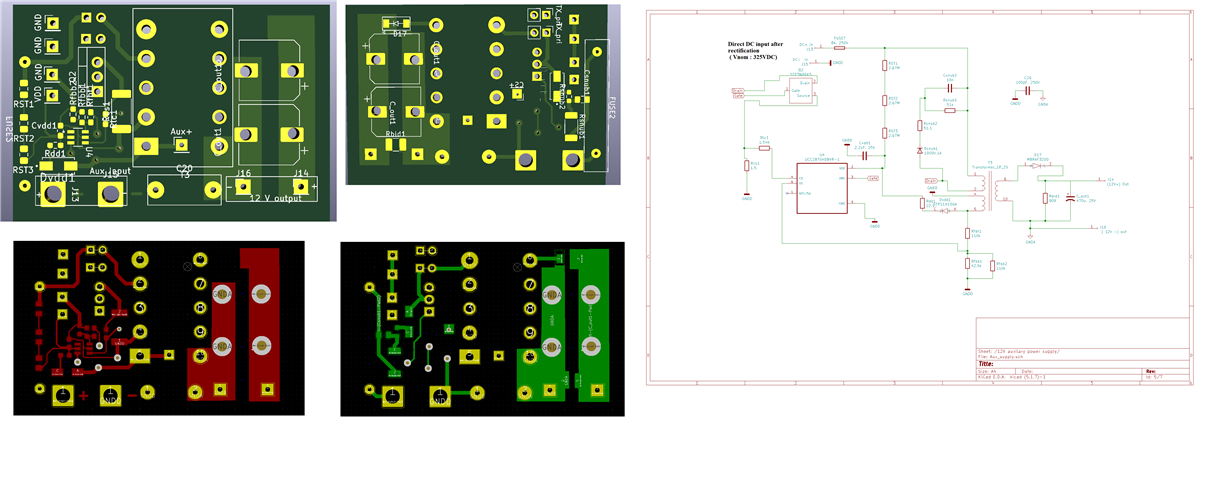

Our customer is using the UCC28704 flyback controllers and upon testing their board it just blew up. They are using an input of rectified DC, the input voltage AC they measured was 234V, and they have a rectifier circuit before the input. They are using it as an auxiliary power supply 12V output for DC-DC converter. Please suggest a workaround for the failure encountered, refer to the screenshot below.

Regards,

Carlo