Other Parts Discussed in Thread: BQ76200, BQ76940,

Hi

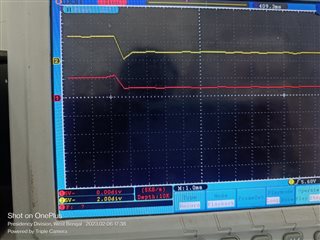

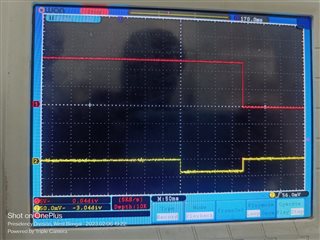

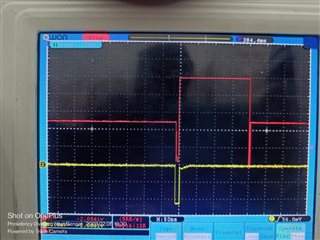

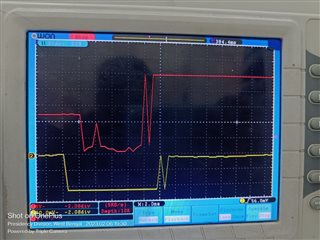

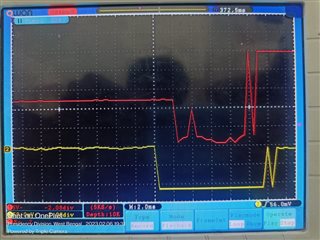

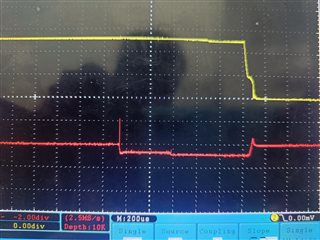

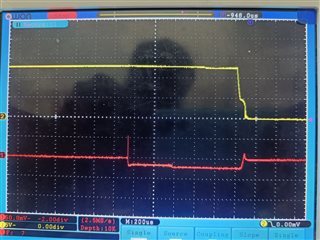

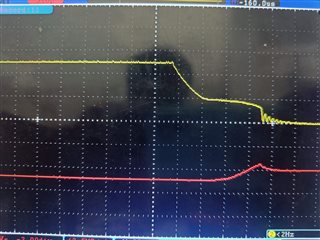

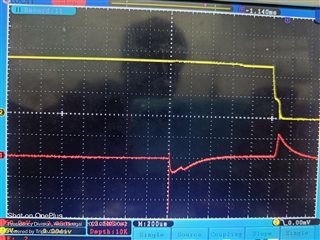

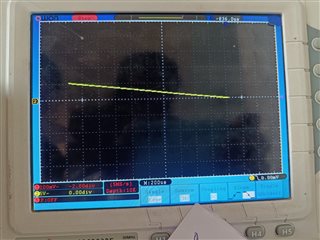

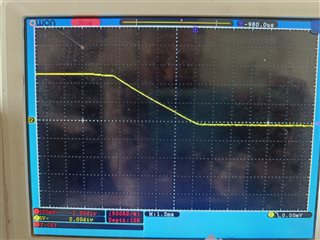

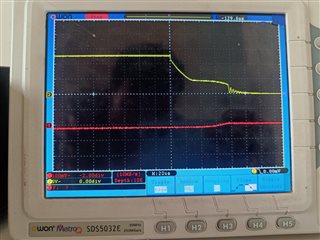

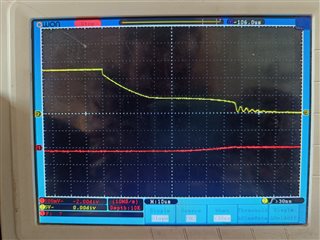

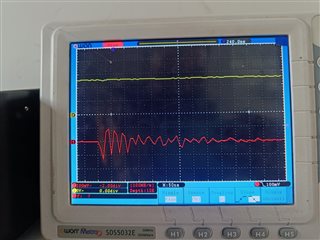

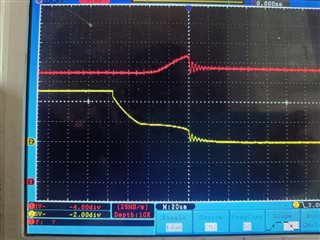

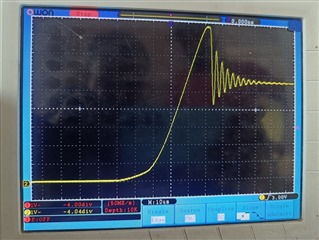

I am Saikat Jana I am working on BMS and Battery Pack Design and for that we are using BQ7791501 as protection IC all the other protection related to the battery pack is working fine (OCD,over temperature, Over Voltage , Under Voltage ) but short circuit is not working.

Process for Short Circuit Test - Short Pack+ and Pack-

Result - Discharging MOSFET get damaged every time

We need to release our product by February and we already have pre orders for that but without short circuit feature we will not able to release the product.

Please help us to release the product as early as possible and me know what tech details I need to provide, ckt-15s (3).pdfHY4008B.pdf

Thanks in Advance

Saikat Jana