Hi Team,

Can you please help answer the inquiry below?

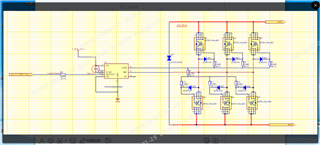

When using LM74502-Q1 to drive the back-to-back MOSFET, after a period of time, use a multimeter to measure the resistance of the gate pin to the SRC pin, and it is found that the resistance decreases to 10 ohms, but the chip can drive the mosfet normally.

Can you help me understand why? thank you.

Regards,

Chase