It is found when our master (MCP2221) communicates with UCD90320 via PMBus, sometimes the PMBus was hang as the SDA kept low. Not sure what happened on this.

Could you please check the below experiment data and see whether there is any method to access the DPM status or analyzing the issue? Thanks.

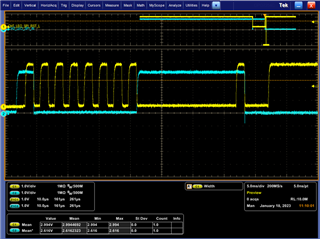

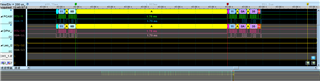

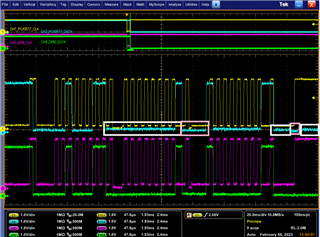

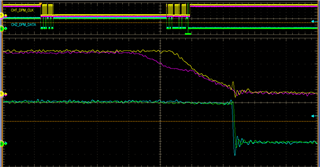

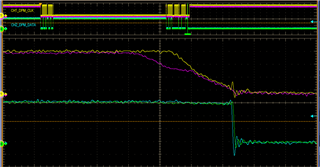

1. As the issue happened, the DPM_I2C bus hang, and further the DPM shows strange behavior. (the output pins seem not working as the designed logic, such as the lower channel on the LA waveform)

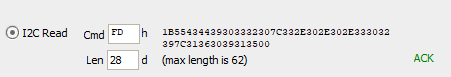

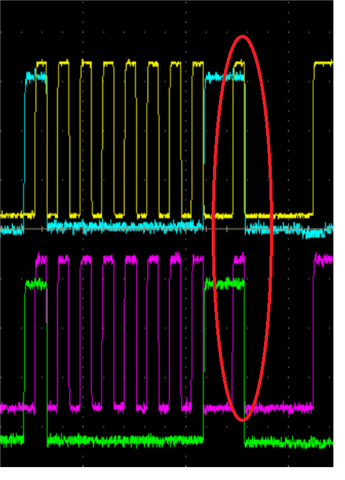

2. It can be seen the i2c not getting a STOP on the interface.

3. As the green (SDA on master side) and blue (SDA on DPM side) signal, there is PCA9546 between the master and DPM side. The DPM seems driving low earlier. Meanwhile, when the SDA trace broken out by the wire, the SDA on DPM side is still low.

4. pleaes refer to the attached file for the traffic transaction between MCP2221 and UCD. (open with Acute LA tool.)