Other Parts Discussed in Thread: TPS389006-Q1, TPS389006

Hi there,

As the TPS6594-Q1 has a generic safety manual which is also valid for the TPS6594133A.

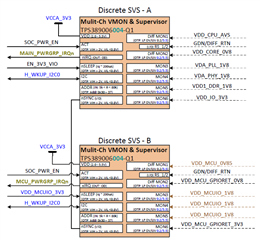

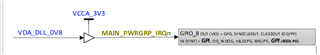

however, in the PDN-3A, tps6594-Q1 has some connections with TPS389006-Q1.

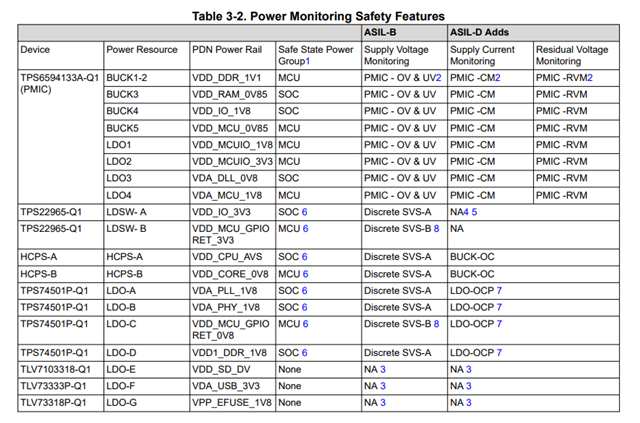

Compared with previous PDN, The use case of the TPS6594-Q1 is changed because of different power rails allocation and monitoring of IRQs from two TPS389006-Q1;

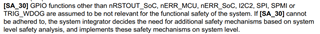

Where can we find a detailed description of these changed features, such as Safety Mechanism related to TPS389006-Q1?

BRs,

Shubiao