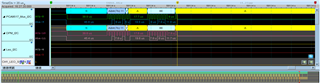

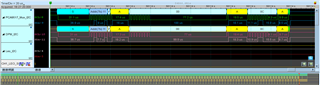

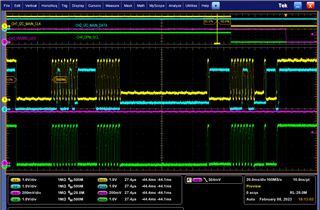

The following is the snapshot as the issue happening. The waveform shows long clock low driven by the master with 59ms; which impact the time period of ACK to repeated-start and then ACK to ACK time period.

As the cursor showing, the 35 ms after the ACK complete, The UCD seems working abnormally. (as some enable output driven by UCD seems not working as expect)

To zoom in the waveform, the master write command of 0x8E, and then UCD ACK it. Further the clock was driven low with 59 ms.

in the previous command of 0x8E, the master writer 0x00 and 0x0C onto the UCD. The waveform shows very long clock stretching time of 77us. Comparing with overall the other transactions, the other transactions with UCD has only 10~20us of clock stretching time.

We are not sure whether there was something wrong already inside UCD during this transaction?

As the following waveform, the master is going to write the 0x00 and 0x0C with longer clock stretching period (~77us).

As this issue, seems few checking items with you; though the master seems driving too long on the ACK to repeated-start period.

1. Does the DPM have problem on the longer clock stretching time (~77us)?

2. What would possibly happen as the UCD getting a very long ACK to repeated-start period (~59 ms)?

3. As the SMBus time out (suspecting the 35 ms is the time out condition), should UCD still work well on its FW defined logic? It is not wished the SMBus transaction can impact the other function out of the SMBus function.

4. If the suspect of 35 ms is correct, can UCD not assert the time-out behavior in 35 ms? i.e. We wish the UCD do nothing different as the SMBus running over 35 ms clock low.

The master is MCP2221 in this case.

Thanks for your attention and kindly suggest if there is any.