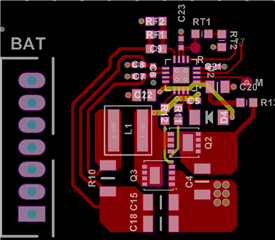

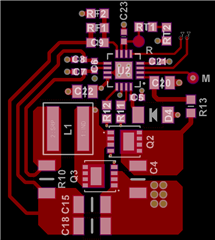

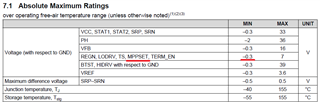

Other Parts Discussed in Thread: LM234, TPS63802, LMR14050, LMR16030

Hi.

Could this be revised by an engineer of Texas Instruments?

I'm open for tips and suggestions.

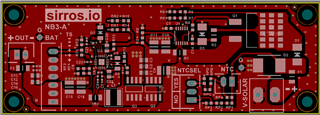

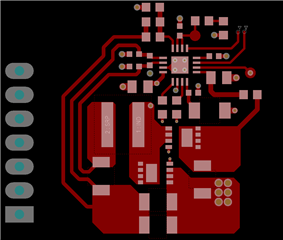

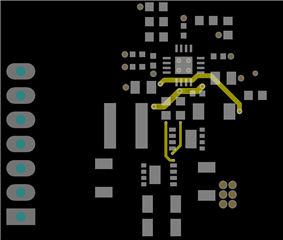

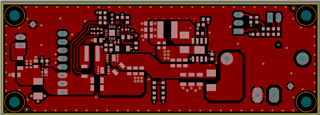

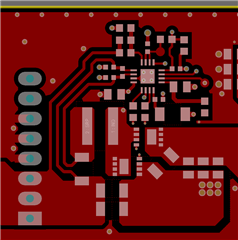

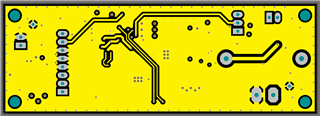

The initial schematic is attached.

MPPSET PIN RESISTORS

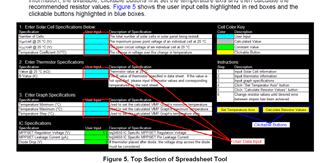

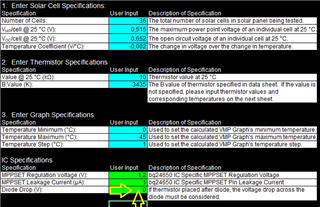

It will be initially considered a 36-cell solar panel with a MPP (maximum power point) voltage of 18.54V. 3 resistors will be used to make a divider between the solar panel voltage and the MPPSET pin of BQ24650, 3 resistors to give more flexibility for future combinations. A resistor divider that when the solar panel has 18.54V (MPP voltage), the MPPSET pin has 1.2V.

Resistors relation = (18.54-1.2) / 1.2 = 14.45

Resistors = 4.7K and 68K (68K + 0R)

The tolerance of the resistors will be 0.1% (4.7K and 68K)

Vmpp(min) = 1.2+1.2*( (68*0.999) / (4.7*1.001) ) = 18.527V

Vmpp(typ) = 1.2+1.2*(68/4.7) = 18.562V

Vmpp(max) = 1.2+1.2*( (68*1.001) / (4.7*0.999) ) = 18.596V

VFB PIN RESISTORS

VBAT = 2.1 + 2.1 * (Rup / Rdown)

It will be used a Li-ion battery with 4.2V floating voltage, so the resistors just need to have the same value. At first, it will be used 2 resistors of 47K with 0.1% tolerance.

Leakage current into VFB pin = 100nA max

SHUNT RESISTOR

SRP-SRN current sense voltage = 40mV +- 3%

40mV / 2.5A = 40 / 2.5 = 16mR

Shunt commercial value = 15mR 1%

40mV / 15mR = 2.66A

I_charge(min) = (40*0.97) / (15*1.01) = 2.56A

I_charge(typ) = 40/15 = 2.66A

I_charge(max) = (40*1.03) / (15*0.99) = 2.77A

(2.77^2) * (15*0.99) = 114 mW, can be used a 1206 resistor of 1/2W

INDUCTOR SELECTION

Initially it will be considered the inductor below, which is already used by us in another board:

Inductor microHenry, SMD, 10uH, +-20%, 5.2A current rating, 9.1A saturation current, shielded, 45.76mOhm max, -55°C ~ 155°C, 8.5x8x5mm, ETQ-P4M100KVK (Panasonic).

The maximum inductor ripple current happens with D = 0.5 or close to 0.5. Usually inductor ripple is designed in the range of 20% to 40% of the maximum charging current as a trade-off between inductor size and efficiency for a practical design.

I_ripple = V_in * D * (1-D) / ( fs * L )

I_ripple = 27.57 * 0.5 * (0.5) / ( 600000 * 10*10^-6 )

I_ripple = 1.15A

I_sat >= Ichg + 0.5*(I_ripple)

I_sat >= 2.77 + 0.5*(1.15)

I_sat >= 3.35A

Ok, the inductor chosen has an I_sat of 9.1A. Maybe it can be replaced by a smaller inductor with smaller saturation current, to reduce the size of the solution.

RESISTORS AT TS PIN

It was considered the use of the thermistor 103AT-2, and a safety charge temperature from 0°C to 45°C

RTHcold(°0C) = 27.28K

RTHhot(°45C) = 4.911K

VREF = 3.3V

VLTF = 73.5% of VREF (3.3V) [typ] = 3.3*0.735 = 2.426V

VTCO = 45% of VREF (3.3V) [typ] = 3.3*0.45 = 1.485V

RT2 = ( VREF * RTHcold * RTHhot * ( (1/VLTF) - (1/VTCO) ) ) / ( (RTHhot * ( (VREF/VTCO) - 1)) - ( RTHcold *( (VREF-VLTF) -1 ) ) )

RT2 = ( 3.3 * 27280 * 4911* ( (2.426) - (1/1.485) ) ) / ( (4911 * ( (3.3/1.485) - 1)) - ( 27280 *( (3.3-2.426) -1 ) ) ) = 82083 Ohms

RT2 commercial = 82K

RT1 = ( (VREF/VLTF) - 1 ) / ( (1/RT2) + (1/RTHcold) )

RT1 = ( (3.3/2.426) - 1 ) / ( (1/82000) + (1/27280) ) = 7.374K

RT1 commercial = 7.5K

MPPT TEMPERATURE COMPENSATION

The compensation for the ambient temperature of the solar panel is still not included, could the LM234 be supplied through the rail "LT-VOUT" of my schematic?

I have some doubts.

(1) How to calculate or, for my case, what should be the value of the feedforward capacitor, C17

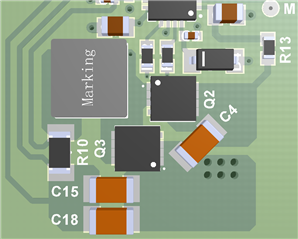

(2) For transistors Q2 and Q3, AO4484, should I replace them with others with a bigger package like the TO-252 (DPAK)? Or are they suitable? Because by reading the datasheet of BQ24650 I ended up understanding that it drives the Mosfets with small Vgs voltages, not like ~12V Vgs drive.

Regards,

Jeferson.