Other Parts Discussed in Thread: TPS7A94, TPS7A21, TPS7A57

Thank you for your help.

I am currently thinking of using TPS7A2033PDQNR to generate 3.3V.

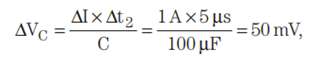

The recommended capacitance range in the specifications is 1uF-200uF, but we are considering how much capacitance to use in our actual application.

We would like to keep the load output current variation to a maximum of 150mA and the voltage variation within 0.8057mV. This is because one of the 3.3V power supply loads is using an AD converter, which is converting at

3.3V, 12bit.

For the above application, what capacitance value should I set for the capacitor?

Also, in determining the capacitance value, could you please provide some kind of calculation formula?

In addition, please tell us if there is anything we should be careful about the capacitance of the input capacitor when using an output capacitor with a large capacitance.

Thank you in advance.