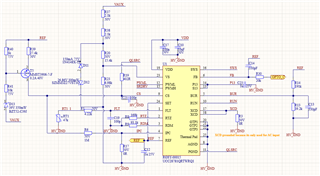

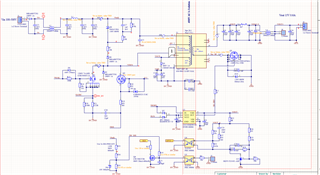

Other Parts Discussed in Thread: ATL431, TLV431, , PMP22322, , TL431, UCC5304, UCC28782, UCC28C56H

Hello TI,

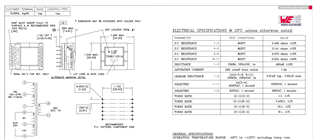

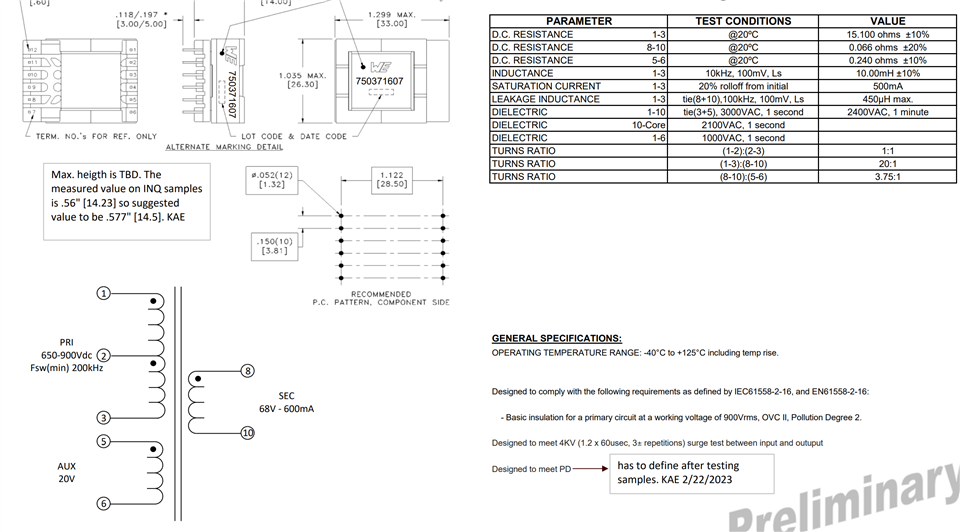

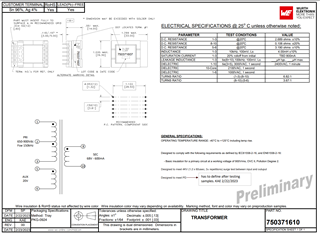

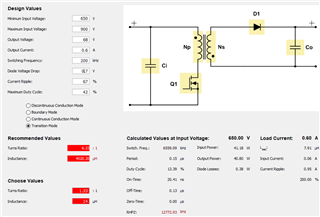

We have followed your EVM schematics and made a test board which does not start. The custom transformer is not made yet so we are using this off the shelf part just for trying out, pinout is different so we used short wires to connect correspondingly (attached datasheet).

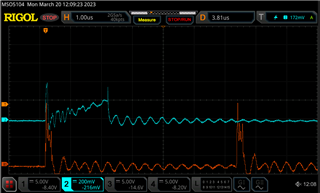

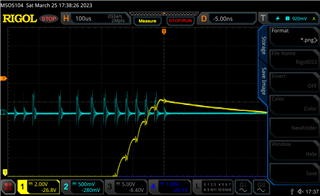

Our PSU currently only provides 120V max so thats what we are testing at right now but i know this design should start at 100V, right? It draws 0mA. I have placed 1k load at 15V output node.

How can we troubleshoot this? What nodes should we measure?

P.S. We know that AUX is misconnected, that we have considered when mounting the transformer and mounted it correctly.