In the datasheet of UCC28180D, the minimum level of soft over current limitation is -0,259V.

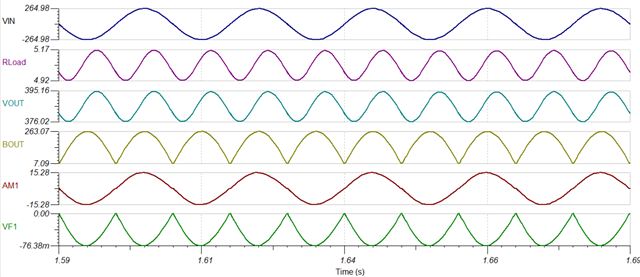

When we simulate in Webench with UCC28180 transient model, with -150mV apply in pin 3 (to pin 1), the line current begin to be distored at the pic of the line current sinusoid. it's the beginning of the action of the SOC limitation of the UCC28180D. The problem is that it acts at a lower level than the minimum value specified in the datasheet. It begins to act at near -150mV whereas the minimum value of SOC limitation should be -0,259V.

We visualize the same defect on a cabled printed circuit board with component values.

How do you explain that?