Hi Experts,

I am posting this on behalf of the customer. Here it is below.

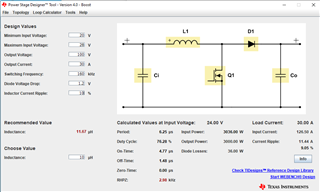

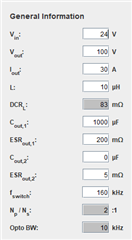

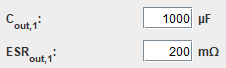

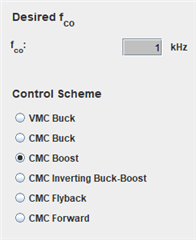

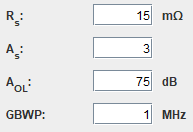

I'm designing a boost converter based on UC3842 as in the pdf file attached. It is showing instability when in full-load operation. Could you please help me to set up the right value for the compensation network? In a few words this is the problem:

the output voltage is regulated to 100V as I want.

The duty cycle in CCM should be 0,76 with an input voltage of 24V.

In steady state (Vout 100V and Iload 4A) on my scope I see 3 consecutive cycles with the maximum duty (limited by the PWM controller to 0,92) and 1 cycle at minimum duty (less than 0,1).

After that, the next pattern is the same, and so on.

The switching frequency is 160kHz.

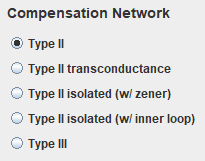

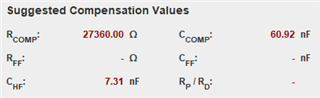

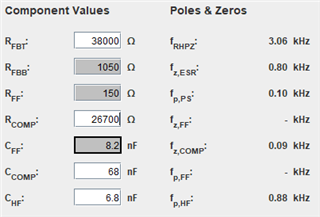

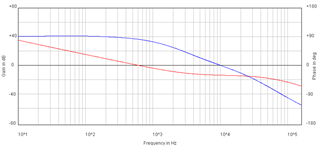

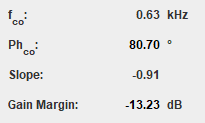

I guess that the compensation network is wrong (R and C are connected to pins 1 and 2 of the UC3842). Probably both pole and zero are not in the right place in the Bode diagram.

Unfortunately on the datasheet, only a flyback calculation procedure is shown. I would like to have an example calculation related to a boost converter.

Thank you in advance.

Best regards,

Jonathan

Best regards,

Jonathan