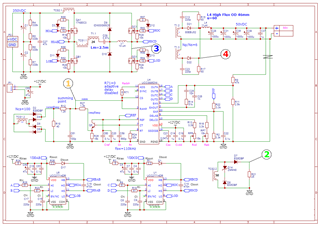

Other Parts Discussed in Thread: UCC2895

Hello,

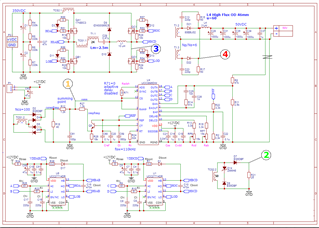

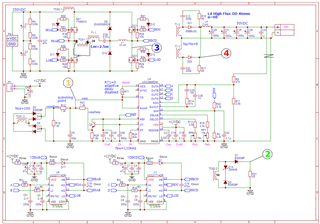

I am designing a CMC PSFB converter based on UCC3895. I ran into a problem with cycle-by-cycle current limiting.

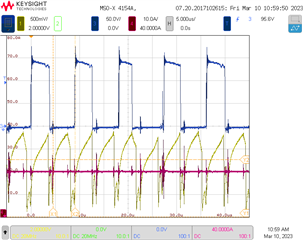

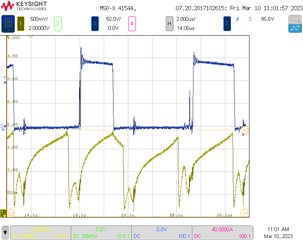

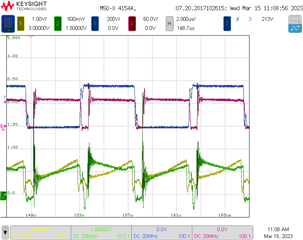

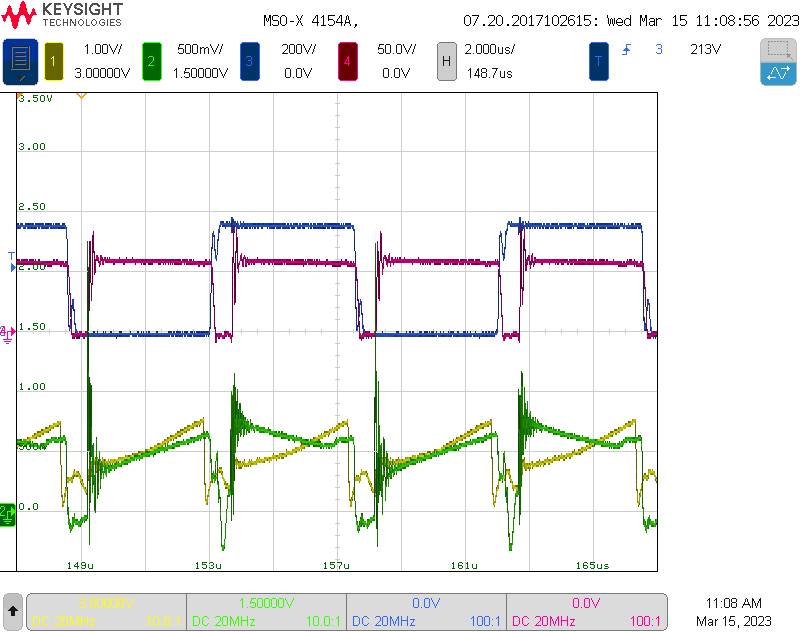

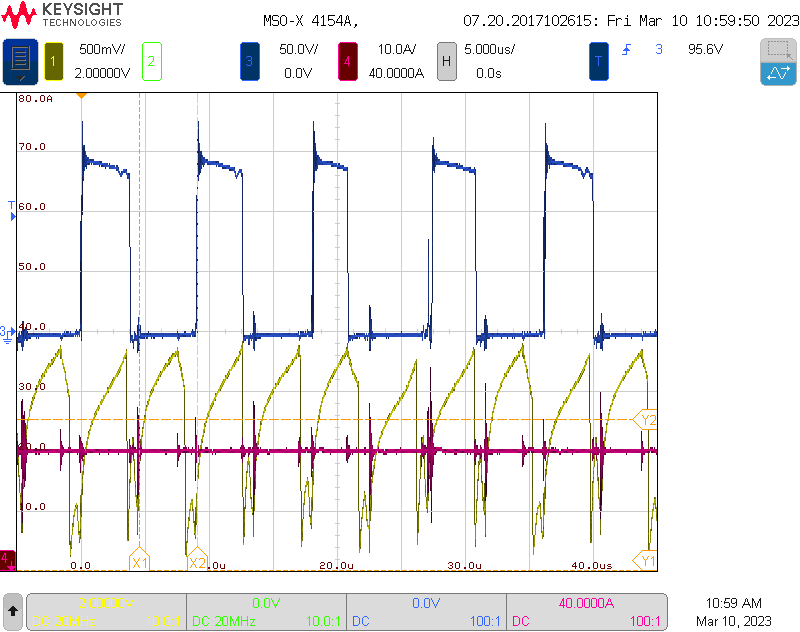

When the voltage at the CS pin reaches the 2V threshold, the duty cycle starts to change rapidly and asymmetrically. This causes audible noise and could even lead to primary TX saturation (in this case 2.5V threshold kicks in, restarting the IC).

I expect that the duty cycle should change smoothly and symmetrically, reducing the output voltage when the load resistance decreases, thus limiting the output current. But that occurs only when the load resistance is too low, when duty cycle is already around 55% and less. From ~55% down to ~0% duty cycle changes smoothly and symmetrically. From ~80% down to ~55% duty cycle changes rapidly and asymmetrically.