Hello Team,

I used Webench to simulate TPSM63610 (FPWM mode) and I wonder why the efficiency is better for higher Vin.

This is something I did not expect. Can you explain, please?

Thanks and Best Regards,

Hans

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello Team,

I used Webench to simulate TPSM63610 (FPWM mode) and I wonder why the efficiency is better for higher Vin.

This is something I did not expect. Can you explain, please?

Thanks and Best Regards,

Hans

Hello Hans,

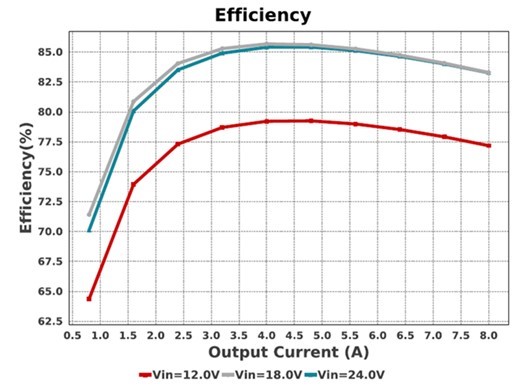

Can you please share the Webench export for review? On my end, I simulated the default design and got the following chart in the Export section. The chart below aligns with what is to be expected since increased input voltage for a fixed output voltage results in more MOSFET switching losses.

Webench design: https://webench.ti.com/appinfo/webench/scripts/SDP.cgi?ID=755D6FDF69C28330

Regards,

Jimmy

Hi Jimmy,

yours look good. Here is my odd design: https://webench.ti.com/appinfo/webench/scripts/SDP.cgi?ID=EA2AD4BD02F85DB5

Thanks and Best Regards, Hans

Hi Hans,

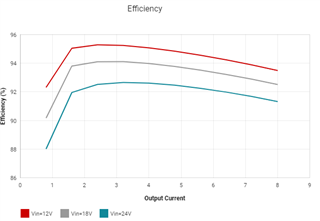

I was able to confirm that I see this issue when generating 1.2V output design.

I then proceeded to check at different low output voltages and was able to get good data down to 1.8Voutput.

Generating a design below 1.8V showed abnormal high efficiency for higher input voltage which should not be the case.

I will look into this with the simulation team to see what the issue is.

For now you can either reference the 1.8V output design or better yet order the EVM and evaluate the IC on bench.

Thank you for bringing this to my attention.

Regards,

Jimmy