Hi,

I want to use BQ76952 in my project. Battery voltage is 48V. In this project i am going to use gate driver.My concern is, BQ76952 uses charge-pump technology so,CHG DSG pins will have a battery voltage+5/10V voltage. (5V or 10V can be selected with registers). But gate driver input pins are capable of maximum 20V.

- Can I disable charge pump and use DSG-CHG as an logic level pins? (I have researched that and I don't think it is possible but I want to ask either)

- I think about analog circuits to accomplish that (opamp comparator, resistor divider etc.) but I couldn't find any suitable circuit for that. Do you have any idea for that?

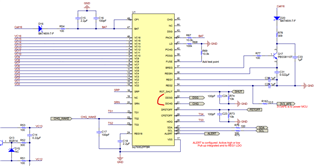

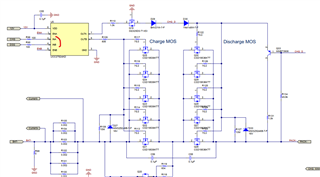

- I have examined TIDA-0102216 refence design. In this reference TI used gate driver. Gate driver charge control signal comes from BQ76952 DCHG and gate driver discharge control signal comes from DDSG. I didn't understand how this configuration works as an DSG and CHG pins. For example if there is short circuit will DDSG be low? The circuit scheme that i talk about is here. And i just found the two explanations of DDSG, DDCHG working with CHG and DSG. I will appreciate if you share any documents about that situation.

Here is a explanation :

Reference design gate driver and control signals:

Thank you.