Mike,

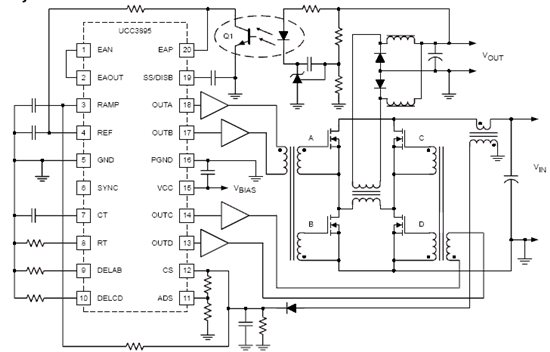

Our customer Emerson using our ucc3895 and add some external circuit for the phase shifted full bridge synchronous rectifier ,they find the OUTA positive duty cycle have a little difference to OUTD ,OUTB and out OUTC also have the same phenomenon,

There difference is about 300ns at 65kHz operation frequency. That means that the OUTD may have 300ns more positive duty cycle than OUTA each period. Is this phenomenon reasonable? Customer told me this issue only happens at close loop. There is no problem at open loop.

Emerson want us give one training about the phase shifted full bridge application to them, including the main topology and design tips and consideration, and simulation. Do you have any material about the phase shifted full bridge can share to me?

Best Regards

Swing Jiang