Other Parts Discussed in Thread: BQSTUDIO

Hi,

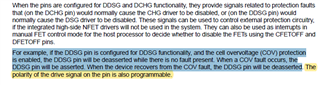

I want to use the BQ76952 AFE to automatically control the charging(DCHG) and discharging(DDSG) FETs based on the faults and recovery from the faults. I'm thinking that I can do that by configuring DCHG Pin Config Register & DDSG Pin Config Register with pin function enabled (PIN_FXN1–PIN_FXN0 : 2 for selecting DCHG & DDSG). I've tried the configuration mentioned in the attached document. I'm able to create the faults and recover, but that doesn't seem to affect the DCHG and DDSG FETs. DCHG remains high all the time after the configuration even with faults. Please help me resolve this issue or correct me if my understanding of this functionality itself is wrong.

(BMS protection, faults, recovery has been independently tested for voltage, current, temperature, short circuit, etc)