Hi Ti experts,

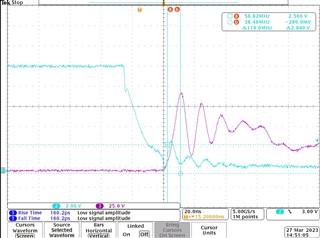

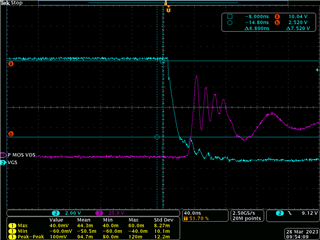

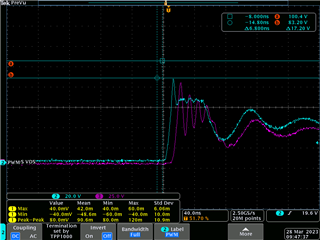

Here is a driver problem that needs your help. Our team designs a 24V to 24V isolation flyback in load 2A. There is a significant spike on Vgs when it is already turned off.

I am trying to use the snubber, cap, and zener to clamp the spike voltage, but it doesn't work. If TI experts can support me with some tips, I will appreciate it.

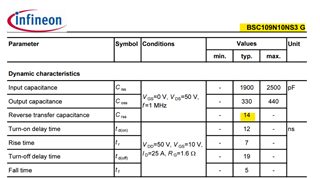

Parameters:

Vin: 21.6~26.4

Vo:24V

Load:2A

fs=266kHz

As below you can see, the Vgs is already down to zero and then turn to 2.56V. I am not sure if it has been through Vgth.