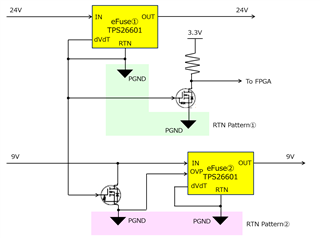

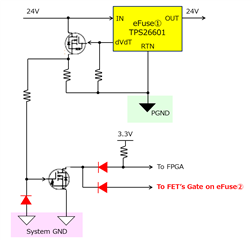

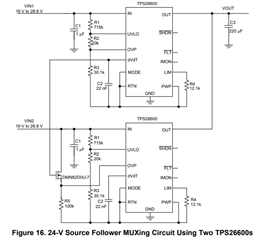

Application note: slva811a is described the solution on OVP disable from FET, please refer page 14 and attached below.

https://www.ti.com/jp/lit/an/slva811a/slva811a.pdf

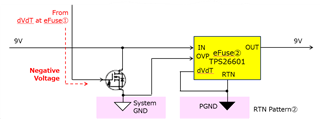

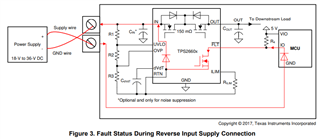

When above case, please let me know about dVdT operation on reverse input supply connection.

(Condition is Application note: slva934a, page 3)

https://www.ti.com/jp/lit/an/slva934a/slva934a.pdf

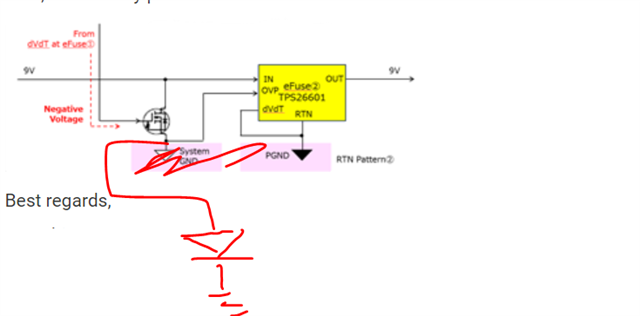

They are concerned that if the dVdT voltage swing negative and the gate voltage of the above FET also swing negative, the VGS voltage may exceed the maximum rating.

Best regards,

Satoshi