Hi team,

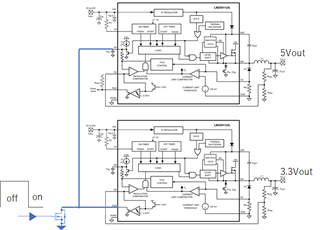

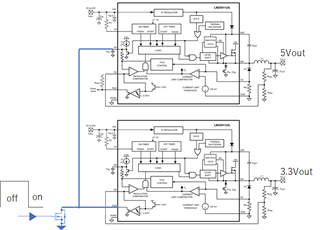

3.3V and 5V are generated with the attached circuit configuration.

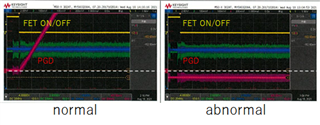

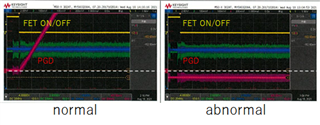

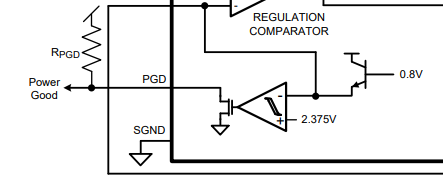

Even though 3.3V is being output, PGD on the 3.3V side does not become High-Z and has a negative voltage.

What causes PGD to be biased to a negative voltage?

Best Regards,

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

3.3V and 5V are generated with the attached circuit configuration.

Even though 3.3V is being output, PGD on the 3.3V side does not become High-Z and has a negative voltage.

What causes PGD to be biased to a negative voltage?

Best Regards,

Hi Sir,

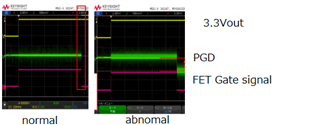

Left picture and right picture is both output of 3.3V PGD pin?

Thanks

Colin

Hi Sir,

I turned off this ticket temporarily. When you reply me, we can restart this conversation.

Thanks

Hi Colin,

Yes, both pictures are 3.3V PGD.

PGD is a negative voltage on the abnormal side.

Best Regards,

Hi Sir,

In abnormal picture, we can see that the PGD has been negative when FET on. I am afraid PGD is pulled to negative voltage by other circuit. Could you share the schematic to check further?

Thanks

Colin

Hi Colin,

The PGD is only connected to SS and FET.

The PGD is negative voltage even if FET is removed.

No circuits are using negative voltages.

It looks like the PGD is driven to negative voltage inside the IC.

Hi Sir,

Actually the PGD pin is internally connected to the drain of an N-channel MOSFET switch. When there is no output. the PGD pin is pull down to GND.

Did you have a test about PGD is negative voltage that LM25011 working alone?

Thanks

Colin

Hi Colin,

Yes, PGD is negative voltage even when it working alone, but this phenomenon is observed our customer board.

When RT is bigger and On-time is longer in the abnormal product, the phenomenon become to disappear.

Conversely, when RT is decreased in the normal product, PGD become to have a negative potential.

Can you think of any reason?

Bes Regards,

Hi Sir,

Could you conduct a experiment about connecting PGD pin to outside 3.3V with a pull up resistor 10k and see whether there is negative voltage on PGD? Other thing is that keeping GND of probe is definitely a 0V, because I see there is lots of noise on PGD pin in abnormal picture.

Thanks

Colin

Hi Colin,

The requested test has already been done, but it was same result.

Since the voltage range is narrow, you will feel the noise is large.

Is there any reason for the negative voltage to be output from the internal circuit of the IC?

Best Regards,

Hi Sir,

Internal circuit of the IC can't output negative voltage and reference of IC is GND. I doubt whether GND of customer board is actual a 0V.

Could you check that?

Thanks

Colin

Hi Colin,

This is the waveform when using FET.

When the FET is ON, PGD is 0V, and when the FET is OFF, PGD becomes negative.

Normal and abnormal were confirmed by changing Ron with the same IC.

Hi Sir,

Could you share the schematic and lay out for further check?

Colin

Hi Hirotsugu,

Please put a 10k resistor between SS pin and PGD pin.

Also I want to confirm that whether test point of V_PGD is PGND or AGNG, I would suggest test point is AGND.

Another thing I want to confirm is that when PGN is negative voltage, whether output of U41 is normal(5.5V).

Thanks

Colin

Hi Colin,

Please do not publish schematics.

I would like to exchange private messages.

Hi Colin,

Thanks for your immediate response.

I will try 10kΩ.

I would check the GND used for the test points.

U41 on the 5V side does not work when PGD is negative.

If I cut the connection with PGD, U41 works and outputs 5V.

Best Regards,